●クラスタテスト

被検査基板上には、JTAGテスト対応デバイスと非対応デバイスが混在している。そのようなボードにおいて高い検査カバレッジを実現するためには、JTAGテスト対応デバイス間のインターコネクトテスト以外にも検査範囲を広げることが重要である。

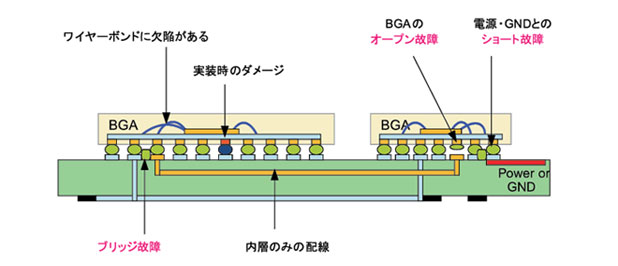

業界スタンダードの『JTAG ProVision』では、JTAG非対応デバイスの部品ライブラリが10万種類以上提供される。この部品ライブラリには、部品ごとの入出力ピン、電源ピン、GNDピンなどのピン属性とロジックの真理値表が含まれている。クラスタテストでは、この部品ライブラリを使ってテストプログラムと合否判定基準が自動生成される。JTAG対応デバイスから実際に周辺の回路を動作させてテストを行うため、図9のように基板上のはんだ不良、はんだブリッジ、部品未実装、JTAG非対応部品のボンディングワイヤ不良など、典型的な製造不良に対するテストを容易に実行できる。

図9 BGA基板に潜む故障の可能性

このようにJTAGテストでは、JTAGテスト対応デバイスが基板上に1つしか実装されない場合でも、十分に検査カバレッジを得ることができる。

●メモリクラスタテスト

最近特にトラブルが多い部品は、DDRメモリである。JEDECによりパッケージの標準がBGAとなり、高速信号であることから基板の内層のみでパターンが完結することが多い。JTAGテストでは、マイコン、FPGA、DSPなどのデバイスがプローブとして機能するため、物理的なプローブは不要である。メモリクラスタテストを実行するためには、マイコン、FPGAのバウンダリ・スキャンセルからDDRメモリのアドレス、データ、コントロールなどの全信号を制御する必要がある。メモリクラスタテストは、基板上のSRAM、DRAM、SDRAM、FIFOなどメモリに適用できる。

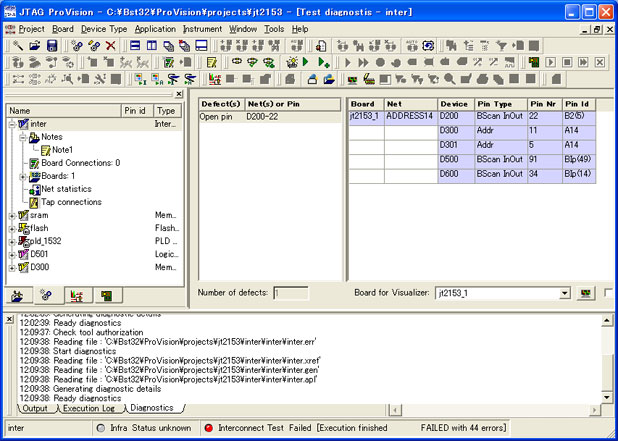

『JTAG ProVision』では、メモリの規格ごとにモデルライブラリが提供されるため、メモリの特性に合わせたテストプログラム、故障診断用の合否判定基準が自動生成される。図10のように、ピンレベルで故障箇所を特定できるため、製造ロットごとの故障傾向を製造にフィードバックすることできる。

図10 テスト診断結果(IC-D200の20番ピンがオープン故障)

●フラッシュメモリ、シリアルメモリ、PLDのオンボード書き込み

JTAGテストツール『JTAG ProVision』では、フラッシュメモリ、シリアルメモリなどの部品ライブラリが提供される。メモリに適したコマンドを考慮したプログラムが自動生成されるため、ユーザーが書き込み用のプログラムを開発する必要がなくなる。『JTAG ProVision』では、メモリへの書き込み、コンペア、消去などを簡単に実行できる。したがって、生産ラインの1つの工程で基板検査から製品のプログラム書き込みまで行うことができる。

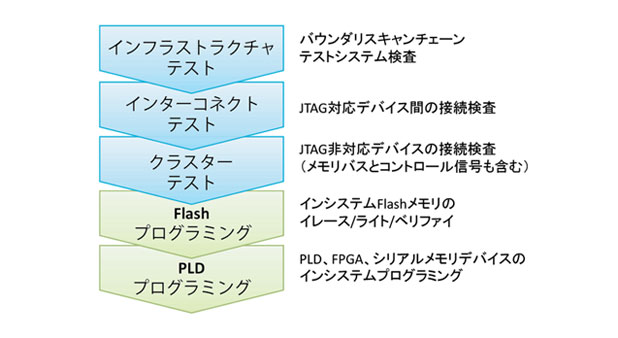

●JTAGテストのシーケンス

図11が標準的なJTAGテストのシーケンスである。『JTAG ProVision』では、テストシーケンスの構築がドラック&ドロップの操作で簡単にでき、1クリックですべてのテストを実行できる。また、テスト結果のログファイルがHTML形式で自動的に保存される。

図11 標準的なJTAGテストのシーケンス

- 会社名

- アンドールシステムサポート(株)

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社