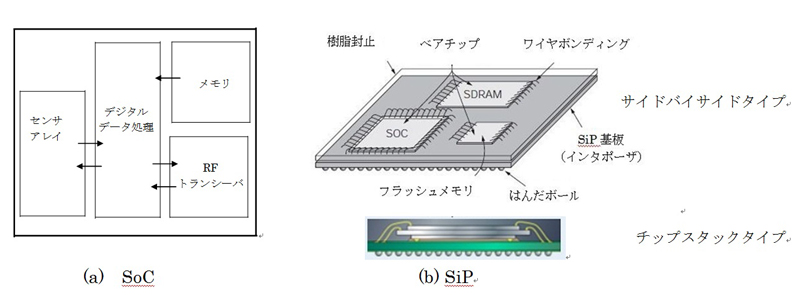

そこで登場してきたのが、SiP(System in package)である。これは一つのICパッケージ内に複数の異種ICチップやアナログ部品を『実装』したものである。SoCとSiPの概念図を図8に示す。SoCでは1チップ内にデータ処理、メモリなど機能の異なる領域を設けるが、製造はモノリシック工程で一体的につくる。 SiPは複数個のICチップや受動部品をインタポーザと称する多層板に搭載したパッケージである。複数部品の搭載の仕方には平らに並べるサイドバイサイドタイプと上に積み上げるチップスタックタイプがある。CPUチップにメモリチップを積んだチップオンチップやTSV(スルーシリコンビア)を形成したチップを積み上げた3次元実装チップもSiPに分類されている。インタポーザには有機のプリント配線板がもっとも広く用いられるが、それ以外にシリコン基板やガラス基板を用いる方法も開発がすすんでいる。

図8 SoCとSiPの概念図

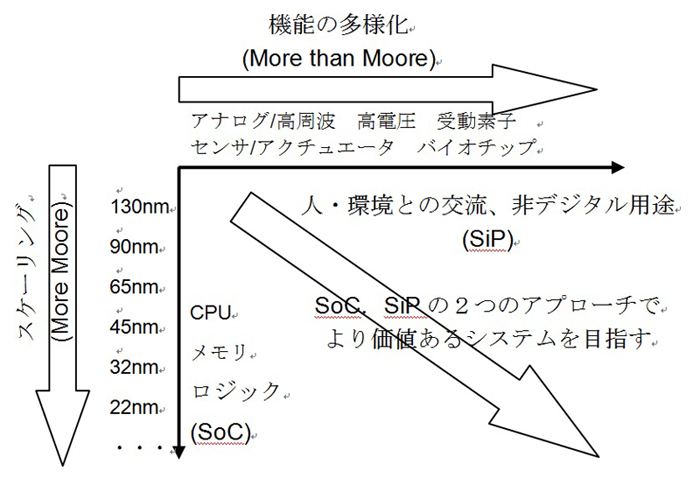

図9 SoCとSiPの目指す方向(2009ITRSロードマップ抄訳)

SiPは品質確認済みの部品を組合わせて作り上げるので、実装基板と同様、開発コストを比較的低く抑えられ、開発期間も短縮できるため、多様な中少量ニーズのシステム開発に向いている。図9はSoCとSiPの今後目指す方向を示したものである(ITRSロードマップより抜粋)。高集積、高性能、高速、省エネルギーの面ではSoCが有利であり、今後もデザインルール32nmから22nmへと高集積化がすすむ。図のMore Mooreは『さらなるムーア(の法則の推進)』を意味している。また、SiPはアナログ、高周波、高電圧などワンチップに集積しにくい機能もワンパッケージに収容する多様化の方向である。そして、このロードマップではSoC とSiPの2つのアプローチで、より価値あるシステムを目指すとしている。図のMore than Mooreは『ムーア(の法則)を超えて(多様化)』を意味するものであろう。

部品内蔵基板

部品内蔵基板はプリント配線板の内部に電子部品(受動部品や能動部品)を埋め込み一体化したプリント配線板である。その概念図を図10に示す。従来の実装基板に搭載されていた受動部品や能動部品の一部をプリント配線板の内部に埋め込んだものである。一見するとマイナーな改良に見えるかもしれない。しかし、部品内蔵基板には従来のプリント配線板の概念を超える要素があり、次世代プリント配線板の一分野になり得るとして世界的に開発研究が活発である。

.jpg)

図10 部品内蔵基板

部品を内蔵することによるメリットは、①実装基板の小型化・高密度化、②パワーインテグリティの向上、である。

今日、携帯、スマホ、タブレットなどモバイル機器は機能が高度化、複雑化する一方で、製品の限りない小型化、軽量化が求められる。現在、部品内蔵基板の多くはモバイル機器に特定機能を持ったモジュールとして採用されている。その最大の理由は小型化・高密度化であろう。部品を内蔵することで実装基板の片面にスペースをつくり、そこにレンズを置いたカメラモジュールのような応用も可能になる。

もう一つのメリット、パワーインテグリティ改善について述べる。パワーインテグリティとはIC電源の安定性の意味である。高速動作するICでは瞬時に大電流がオンオフする。そのとき電源電圧が一瞬変動する。これは家庭でワットの大きい器具のスイッチを入れたとき、電灯が一瞬暗くなるのと同じ現象である。原因は屋内配線が瞬時の電圧変動を抑えるほど太くないからである。モバイル機器には安定した電源が入っている。しかし各ICに至る配線はきわめて細い、さらに、3章で述べた配線のインダクタンスが効いてICがオンになる瞬間、IC入口での電源電圧が大きくドロップし、ICの誤動作を引き起こす。これを防止するのがパスコンと呼ばれるコンデンサである。パスコンをIC近くに置くと、それが電気の溜池として働き、瞬時の電圧変動を吸収してくれる。高速動作するICのほとんどにはこの目的でパスコンが配置されている。パスコンはできるだけIC近くに置く必要があるが、図10の表面実装ではICチップの横に配置するので近づけても10mmくらいの距離は必要となる。部品内蔵基板にしてパスコンをIC直下に置ければ、その距離は1mm前後に縮めることができる。GHz帯の高速ではこの差が大きく、部品内蔵基板の大きな利点とされている。実装基板をモジュール化して、十分小さくできれば、3章で述べた信号線を伝送線路として扱う(特性インピーダンスを考える)必要がなくなるメリットも期待できる。

部品内蔵基板の製造について考える。従来の電子機器やシステムは、①電子部品(能動、受動部品)の製造、②プリント配線板(部品の載っていないベアボード)の製造、③電子部品の実装(実装基板の製造)、④複数の実装基板、入出力装置などを組み合わせてシステムとして完成させる、というステップを踏んでつくられてきた。それぞれのステップは専門メーカーが分担し、ステップに即した検査を行い、品質を保証した製品を次ステップに渡していた。それが部品内蔵基板になると、プリント配線板の製造途中に部品の作りこみや部品実装の工程が入り込むことになる。そのため、製造途中での品質確認がむずかしく、完成品で検査するしかない。部品内蔵基板として完成しても表面搭載の部品がすべて実装されていなければ実装基板としての検査もできない。そのため、工程が複雑化し、部品内蔵用部品の使用などでコストアップとなり、不具合発生時の責任の所在があいまいになったりするという課題もある。

部品内蔵の技術は一般の実装基板すべてに適用可能であるが、上記のようなコストアップその他の課題があるため、実装基板全体を部品内蔵にするメリットは見出しにくい。モバイル機器の高周波モジュールや上記カメラモジュールのように、機器機能の一部を部品内蔵技術を使って1モジュール化するというのが部品内臓基板のもっとも有効な利用法と思われる。このようなモジュール製品への進出はプリント配線板メーカーが目指す一つの方向であるが、それはまた半導体メーカーが目指すSiPのアプローチとも重なり、その境界は今後さらにあいまいになってくるであろう。

放熱基板

省エネ照明として人気のLEDランプの最大の課題は放熱といわれる。白熱電球に比べてエネルギー効率が格段に高いLEDランプでなぜ放熱が問題になるのか。理由のひとつはLEDが非常にせまい場所、半導体接合部(ジャンクション)で発熱すること、もうひとつは半導体であるLEDが高温使用に弱いことである。LEDの発光効率(電力を光に変える効率)が他の光源に比べて高いといっても光になるのは20%弱といわれる。残り80%余りの電力は熱となってジャンクション部の温度を上げる。一般に狭い場所での発熱は放熱が難しい。LEDチップの消費電力は1W程度と小さいが、発熱部が数ミリ角と小さいので熱がこもりやすいのである。LEDランプで放熱が問題となる2つ目はLEDの寿命が高温で使用すると極端に低下することである。ジャンクション温度150℃で寿命4万時間のLEDが、170℃では1万時間に、185℃では千時間(150℃で使用時の1/10)にまで下がるのである。これに比べ、白熱電球はフィラメント温度が2,000℃くらいまで上がるが、フィラメントのタングステンはこの温度にもちこたえる。また、蛍光灯では蛍光管全体から発熱するため温度上昇は問題にならないのである。LEDランプはジャンクション温度が150℃以上に上がらないように放熱設計されている。

半導体の放熱問題はLEDだけではない。一般に半導体チップの消費電力はトランジスタの集積度と動作周波数の両方に比例して増大する。最新の高速、高性能CPUには消費電力が100Wを超えるものががある。家庭用アイロンのワット数は100W程度であるが、表面積はCPUパッケージの10倍もある。放熱面積の小さいCPUパッケージから100Wを放熱して、ジャンクション温度を限度内に維持するのは容易でない。そのため放熱ファン、ヒートシンク、水冷、ヒートパイプなどさまざまな強制冷却の手段が用いられる。強制冷却がむずかしいモバイル機器の設計ではCPUの冷却は常に大きな課題である。

- 会社名

- 小林技術事務所

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社