2.設計でのEMC対策

まず、システム設計と回路や基板の詳細設計の設計段階でのEMC対策を考えます。

構想設計、全体設計の段階では回路とメカの両方を見て、機器のシールドを考えます。現在、電子機器は機器全体をシールドするのは常識となっています。機器のシールドは機器のデザインやコストに大きな影響を及ぼします。全体のデザイン設計を行うとき、ケーブルの張り回しや基板の大きさ、配置場所などを考慮してシールドの方法を考えておく必要があります。この時点でシールドやノイズの問題からも、部品を片面配置にするか、両面対置にするかなどが決まることもあります。特に、できるだけ薄く、軽くしたい携帯機器などでは、シールドのための重量やスペースへの影響は大きいので、初期段階の検討は重要です。

次が回路設計段階です。ここでは、個々の回路について、できるだけ電磁ノイズを発生させないように設計します。また、配線レイアウト設計に対しレイアウト上の注意点を明確にします。電磁ノイズを発生させない設計は、基本に忠実に信号上のノイズを小さくさせることです。デジタル信号なので、許容値以下のノイズは回路動作上では問題ありません。しかし、許容値以下のノイズでも電磁放射の原因になることはあります。また、終端がない配線はアンテナになります。このため、できるだけていねいに終端処理を行います。また、信号の立ち上がり、立下りが早いとノイズが大きくなるので、高速信号では、タイミング的に問題にならない程度の信号に直列抵抗を挿入して信号の立ち上がり、立下りを遅くすることも有効です。

基板の層構成、電源・グランドの安定化のための検討も設計の早い段階で行います。基板の層数を多くし、電源・グランドのプレーン層を多くすれば、電源・グランドのノイズは減少し、放射ノイズの低減には有効ですが、基板コストは高くなります。基板の信号を内層で配線し、外層をグランドプレーンにすると外層が電界遮蔽となり、信号からの放射ノイズや外部からのノイズ進入を減少させる効果が得られます。

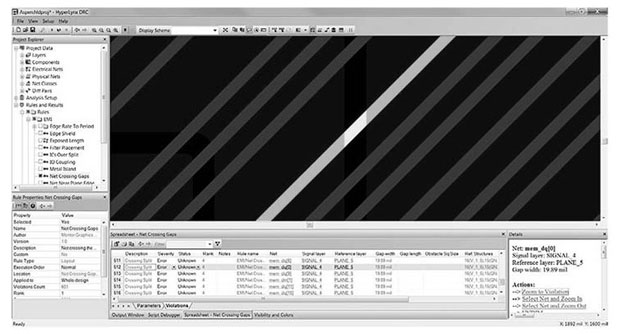

また、特にアンテナや放射ノイズの原因になりそうな配線やプレーン形態、パスコンの配置や配線に対して、基板レイアウト配線への注意を伝えます。回路設計からレイアウト設計への注意事項を伝えたり、この注意事項を守った設計ができているかをチェックしたりするEMIルールチェックソフトがいくつか製品化されています (図5)。設計の最後の段階は基板のレイアウト設計になります。

図5 EMC対策ルールチェックソフト(HyperLinx DRC/Mentor Graphics)

現在の電子機器設計では、基板のレイアウト設計とメカの実装設計が非常に重要になっています。EMI対策でも、この2つの設計が非常に重要です。

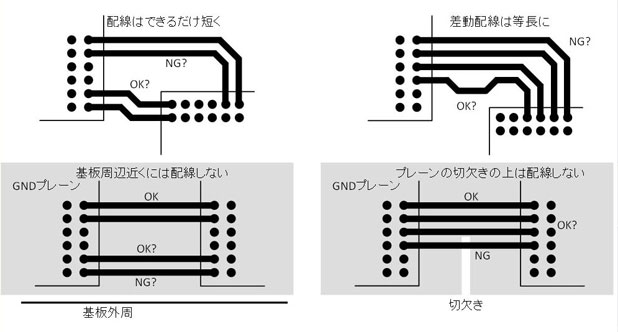

基板設計は電磁放射ノイズの大きさを左右する非常に重要な設計です。しかし、電磁放射に対する設計指針は、信号伝送(SI)に対する明確なルールに比べ、抽象的でわかりにくいものとなっています。たとえば、SI設計ルールでは『バス配線は誤差1mm以内で配線長をそろえること』などと、具体的なルールが決められています。 しかし、EMIルールでは、『バイパスコンデンサは電源ピンのそばに配置すること』とか、『この信号配線に対しては隣り合う層のグランドの切り欠きがないこと』などの設計ルールとなります(図6)。

図6 抽象的なEMC設計ルール

つまり、SIに対する規則は定量的であるのに対し、EMIに対する規則は定性的なものが多いのです。

- 会社名

- (株)日本サーキット|KEI Systems

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社