4.TSVの技術発表動向

アメリカでは1990年頃にシリコンインタポーザ使ったマルチ・チップ・モジュール(MCM-D)が多く現れました。これは現在の2.5次元実装です。

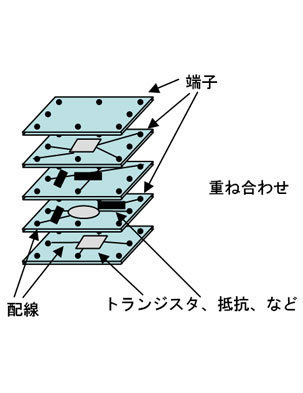

MCM自身は1960年代、IBM System 360でセラミック基板に複数の部品を実装し、モジュールとして基板上に実装したものが初め(図16)で、その後、高周波回路などによくつかわれていました(図17)。

図16 マイクロモジュール

図17 マイクロ波IC

それが、セラミック基板の代わりに安価なプリント配線板や高機能なシリコン基板を使って、SiP(System in Package)を実現する流れが90年代になって出てきたのです。

シリコンインタポーザを使ったMCM-Dはその配線の集積密度の高さや、チップと基盤の熱膨張率が同じで熱応力が小さいこと、放熱特性が良いことなど高性能化では群を抜いていましたが、価格やビアを使っての電源供給の困難さなどの技術的問題がありました。

このため、日、米、欧でシリコンインタポーザビア接続する技術(TSV)の研究開発が進められました。

最近では急速にアジアの研究機関がTSVの開発を進めています。

日本では、超先端電子技術開発機構(ASET)が1999年度から『超高密度電子SI』というプロジェクトを開始しました。

1990年代から2000年代の始めまでは、ヨーロッパを始めとして、各国から学会レベルで、シリコンに貫通ビアをあけて導通を確保したという発表が多くありました。

この頃の発表はTSVに対する個別技術が主体でした。つまり、穴あけの方法、ビアの導通の作り方、シリコン基板の平坦化技術、インタポーザとICチップの接続技術などです。

その後、信頼性、熱特性など、実用化に向けてのアプローチもありましたが、価格の問題があり、特に日本では、一部のハイエンド製品にしかマーケットがないのではないかとの考えも出てきました。

5.逆転の発想

これまで、どちらかというと、TSVは、ICチップの積層による飛躍的な集積度向上を実現する技術として考えられてきました。これは、ICの微細化による集積度の向上が遅く、限界もいわれ始めている中モバイル機器などでは、処理速度の向上とメモリ容量の増大が強く要求されているからです。

特に日本では部品の小型化が得意分野でもあり、ICチップの積層により、ピン数も増えずに大狭量なCSP(Chip Size Package)ができれば、付加価値が上がり、TSVのコストを吸収できるのではないかと考えられてきた向きもあります。

信号の高速化や低消費電力でも同じです。TSVは高価なので、高性能化により、価格をカバーしようと考えていました。

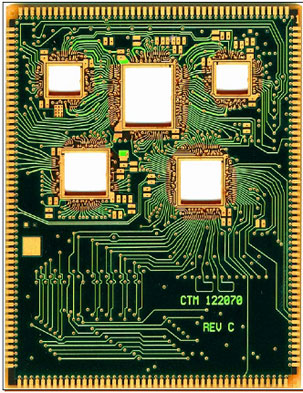

ところが、2010年にXilinx社がTSVを使った2.5次元のMCMを発表し、2011年に製品化しました。

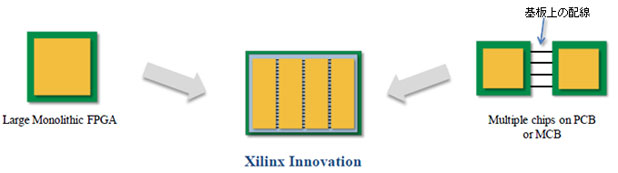

Xilinx社の製品は大きな1チップで実現できる製品をあえて、小さな4チップに分割し、それらを困難な3次元実装をするのではなく、単にシリコンインタポーザの上に平面実装したものでした。

それまでの3次元実装と異なるTSVの応用で、これまでのMCMをTSVを使ったシリコンインタポーザで実現したもので、2.5次元実装と呼ばれるようになりました。

ここでの要点は、大きな1チップでSoC(System on Chip)を作るより、小さな4チップに分割してTSVを使ったSiP(System in Package)にしたほうが安くできるというものでした(図18)。

図18 2.5次元実装のほうが安価,大きなチップと小さなチップの歩留まりの差はMCMコストより大きい(Xilinx社資料)

それまでの常識を破って、既存実装技術で作るよりも、TSVの方が安くできるということで、各社の取り組みが変化しました。

- 会社名

- (株)日本サーキット|KEI Systems

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社