業界コンソーシアムによるUCIe 1.0仕様の全体概要である。

・4月13日付け 3D InCites:Phil Garrou氏ブログ

IFTLE 517: Chiplet Standardization Closer than ever with UCIe

→3月初旬、ASE、AMD、ARM、Google、Intel、Meta、Microsoft、Qualcomm、Samsung、TSMCの印象的な業界グループは、ダイツーダイ相互接続標準を確立し、オープン

チップレットエコシステムを促進する業界コンソーシアムの結成を発表した。

創設企業は、Universal Chiplet Interconnect Express(UCIe)仕様を承認した。UCIeは、パッケージレベルでユビキタス相互接続を確立するために開発されたオープンな業界標準である。パッケージ内のチップレット間の相互接続を定義する。UCIe 1.0仕様は、定評のあるPCIExpress(PCIe)およびCompute ExpressLink(CXL)業界標準を活用するダイツーダイI/O物理層、ダイツーダイプロトコル、およびソフトウエアスタックを対象としている。

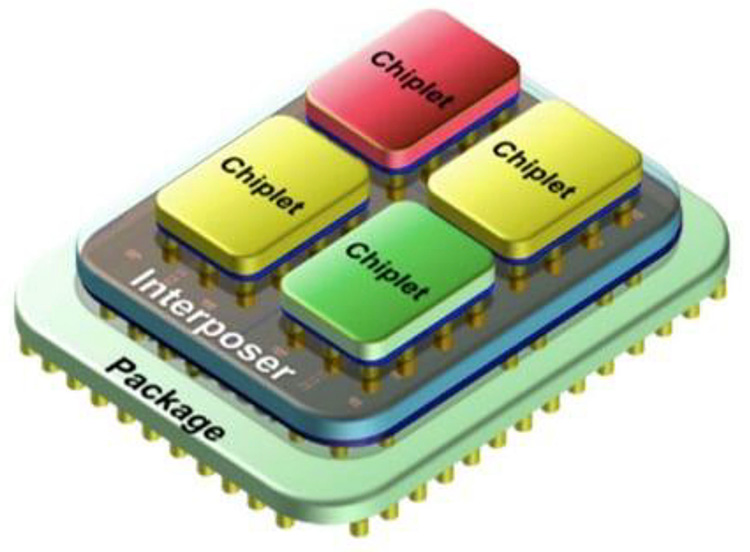

チップレットベースのプロセッサのイメージと課題である。

・Innovative Interconnects: The Future of Chiplet based Processors?

(4月19日付け All About Circuits)

→AMD、Intel、およびNVIDIAなどの世界最大手の半導体メーカーの多くがチップレットに投資している。しかし、異種プロセッサには欠陥がないわけではない(図2)。

図2

チップレットの業界標準により、高まる採用拡大の期待である。

・Paving The Way To Chiplets Chiplet adoption gains with industry standards Different interconnect standards and packaging options being readied for mass chiplet adoption

(4月25日付け Semiconductor Engineering)

→Advanced Micro Devices(AMD)、Intel、Marvell Technology Groupはすでにチップレット技術を採用している一方、他の半導体メーカーは、チップレットの業界標準の作成のおかげでこの次世代のコンセプトに惹かれている。

「常にチップレットを使うべきか、そうすべきでないかという一般的なルールはなく、それはすべて、その特定のアプリケーションに依存する。」と、Googleのadvanced technology development engineer、Mudasir Ahmad氏。「フィードバックを提供するために、各アプリケーションに使用できるモデルが必要」と付け加えた。

チップレット採用の現時点が、具体的にあらわされている。

・Chiplets: Current Status

(5月12日付け Semicondctor Engineering)

→最近の製品は、大きくて複雑なチップレット構造でも確実かつ効率的に設計できることを示している。

ここ数週間、チップレットの分野で多くの興味深い開発が見られた。特にプロセッサセグメントでは、チップレットをベースにした製品がますます多く市場に投入されている。たとえば、AppleとAMDは現在、チップレットを備えたプロセッサを市場に出し、大量生産を行っている。一方で、これは製造業者側で十分な生産能力が構築されたことを意味する。以前は、そのようなボリュームの生産能力はチェーン全体で不足していた。一方、これにより、大きくて複雑なチップレット構造でも確実かつ効率的に設計できることが確認された。ただし、これまでのところ、アプリケーションはユニット数が多いものに限定されている。

UCIeを話し合ったメンバーが示されているが、これら強大な顔ぶれが合意の範囲内で進んでいけるか、注目を要するとの見方である。

・5月18日付け 3D InCites:Phil Garrou氏ブログ

IFTLE 520: Intel Responds to the Universal Chiplet Interconnect Express

→以下に示すメンバー企業によるUniversal Chiplet Interconnect Express(UCIe)の通過により、チップレットの世界での今後の標準化についての話し合いが行われた。 このpowerhouseグループがすべて同じページ合意、だれか他が自前で離れないか? それを疑っている(図3)。

図3 Members of the Universal Chiplet Interconnect Express consortium

UCIe仕様標準への用途拡大に向けた期待である。

・Standardizing Chiplet Interconnects Chiplet interconnect spec paves the way for

wider use Why UCIe is so important for heterogeneous integration

(5月23日付け Semiconductor Engineering)

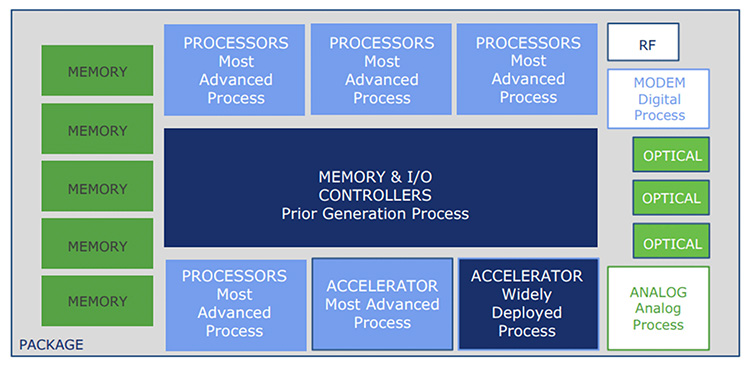

→Universal Chiplet Interconnect Express(UCIe) Specification 1.0は、chiplet技術のより多くの展開を生み出すことを約束している。「UCIeのような標準化された相互接続プロトコルは、chiplet技術の堅牢なエコシステムの主要なイネーブラーとして機能する」とSiemens EDAのverification IP product manager for the IC Verification division、Gordon Allan氏(図4)。

図4 UCIeにより、設計者は将来の半導体開発において、プロセッサ、メモリ、コントローラ、RF、I/Oなどの機能ブロックをチップレットに分離できるようになる(出典:UCIeコンソーシアム)

最先端に近づける手立てとなるのか、中国におけるチップレットへの率直な見方があらわされている。

・Tech war: is the ‘chiplet’ a short cut for China to address its semiconductor self-sufficiency or a wrong turn?

(5月26日付け South China Morning Post (Hong Kong))

→中国の半導体業界はTSMCなどの国際的なファブに遅れをとって数十年とまではいかなくても数年であり、チップレットは中国で人気を博している(※)。

(※ただし、一部の専門家は、チップレットは先端半導体製造技術を“補完”するものであり、それに代わるものではないとしている)

設計から、製造、組み立てまで完結してカバーする必要があるチップレットは。IDMに好適との見方である。

・Who Benefits From Chiplets, And When Experts at the Table: Deploying chiplet

technology Challenges involving reliability, integration and chiplet availability will take time to iron out

(5月31日付け Semiconductor Engineering)

→5人の業界専門家がチップレットの使用について話し合っているroudtable interview。「チップレットは、IPから製造、組み立てまでのプロセスをエンドツーエンドで所有しているため、IDMに非常に適している」と、Keysight Technologiesのvice president and general manager、Niels Fache氏。

光I/Oチップレットに向けた連携の取り組みである。

・Ayar Labs Partners with Nvidia for Optical I/O Chiplets

(6月1日付け EE Times)

→カリフォルニアの光chip-to-chipのスタートアップ、Ayar Labsは、光半導体間通信技術を中心にエコシステムを構築している。同社はNvidiaと提携して、光I/Oを備えた次世代アーキテクチャを開発している。

- 会社名

- Gichoビジネスコミュニケーションズ株式会社

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社