1. はじめに

前回の本誌12月号では「この1年の半導体市場の動きその①」として、先端実装関連について、「技術および市場評論」と「国際会議および展示会」の動きを総括してご紹介した。

今回は「チップレット技術関係」および「3D NANDはじめメモリ関係」についてご紹介する。

2021年10月から2022年9月までの動きについて、以下、それぞれ基本時間順に示していく。

2. チップレット技術関係

半導体をコア単位で製造して、後から「レゴブロック」のように合体させることで1つの製品をつくり出す方式、チップレットへの注目がこの1年でますます高まって、標準化のコンソーシアムの設立に至った。チップレット技術関係の内容および動きについて、以下、基本時間順に辿った。

Moore’s Law先延ばしを支えるチップレットへの期待である。

・Moving from SoCs to Chiplets could help extend Moore’s Law

(11月11日付け EE Times)

→Moore’s Lawが再び限界に達してきていて、いくつかの技術、特にChipletsが、さらに何年も先延ばしするカギとなる可能性。

チップレット標準化の不足が求められたこの時点である。

・Missing Interposer Abstractions And Standards Use of chiplets limited by lack of standardization Interposers still need to be opened to the masses; benefits include more flexibility and fewer aging effects

(11月29日付け Semiconductor Engineering)

→より多くのchipletsの導入が、主流computer生産の断片的なシステムにより制約を受ける。「結果として、これまで実際にこの作業を行った人々だけがvertically integrated guysであり、topからbottomまでstack全体を制御する人々である。そしてどの半導体もそれを心に留めて設計されている」と、Ansysのdirector of product marketing、Marc Swinnen氏。

チップレット間のDie-to-Die(D2D)データ転送に向けたセキュリティIPが打ち上げられている。

・Security IP for Die-to-Die communication between chiplets CEVA launches security IP for chiplet communications

(1月26日付け New Electronics)

→CEVAが、Fortrix SecureD2D半導体intellectual property(IP)を導入し、Heterogenous System on Chip(HSoC)内でのchiplets間のデータ転送を安全確実にしている。Gartner Researchは、chiplets搭載SoCsからのmicrochip売上げが、2年前のわずか$3.3 billionから、2024年には$50.5 billionに増加すると予測している。

インテルにより開発されたUniversal Chiplet Interconnect Express(UCIe)標準、および各社の賛同を得て設立されたチップレットコンソーシアムを巡る経緯が、以下に示されていく。

・Tech giants Intel, Meta, Arm, Google Cloud, AMD, Qualcomm, TSMC and ASE form chiplet consortium

(3月3日付け FierceElectronics)

→ハイテク大手数社が協力、半導体コンポーネントのオープン標準およびAI応用はじめ動かす今後のhandheldおよび高性能computersに重要と見なされるsystem-on-chip(SoC)設計での詰め込み方が推進されていく。オープン標準、Universal Chiplet Interconnect Express(UCIe)は、インテルによって開発され、アリゾナ州とオハイオ州、および米国以外の場所で新しい半導体fabsを構築するため、インテルのintegrated device manufacturer(IDM)戦略に明らかにメリットをもたらす。インテルは、半導体製造を現在非常に大きく重点化されている台湾およびアジア他地域で拡大推進を図っている。

・Intel, TSMC, and Samsung start chip stackingv consortium Chiplet standards consortium formed by industry New standard will spur collaboration on ‘chiplets’

(3月3日付け Taiwan News)

→Universal Chiplet Interconnect Express標準が確立され、chiplets技術の使用に関する新しい業界コンソーシアムによって管理される。Intel、Qualcomm、Samsung Electronics、Advanced Micro Devices(AMD)、Arm、Taiwan Semiconductor Manufacturing Co.(TSMC)、Google Cloud、Meta、Microsoftが、該業界の取り組みをサポートしている。

・Leaders in Semiconductors, Packaging, IP Suppliers, Foundries, and Cloud Service Providers Join Forces to Standardize Chiplet Ecosystem

(3月3日付け 3D InCites)

→Advanced Semiconductor Engineering, Inc.(ASE)、

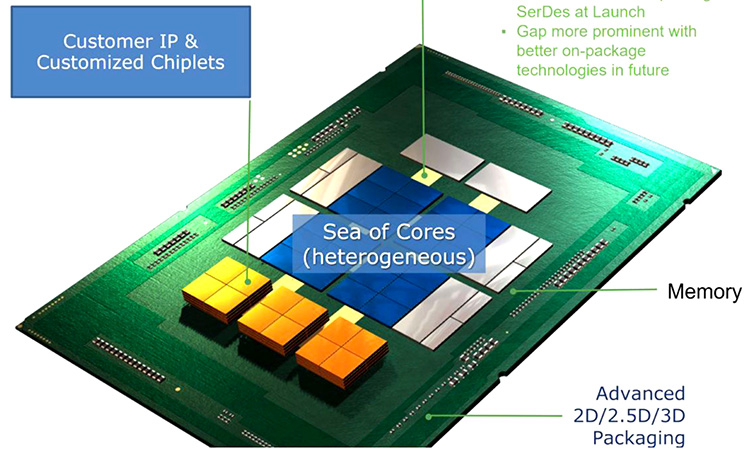

AMD、Arm、Google Cloud、Intel Corporation、Meta、Microsoft Corporation、Qualcomm Incorporated、Samsung、Taiwan Semiconductor Manufacturing Companyは本日、業界コンソーシアムの形成を発表した。 die 相互接続標準を確立し、オープンなチップレット エコシステムを促進する(図1)。

図1

スーパーコンピュータの開発競争にチップレットが入っていく現状である。

・Chiplets Enter The Supercomputer Race Chiplet-based exascale supercomputers become a reality Nations compete on speed using very different compute architectures

(3月17日付け Semiconductor Engineering)

→複数の機関がchiplet技術に基づいたスーパーコンピューティングシステムを開発している。Hyperion Researchは、スーパーコンピュータ市場が昨年の$6.6 billionから今年は$7.8 billionに増加すると予測している。

Universal Chiplet Interconnect Express(UCIe) 1.0仕様登場の1つのインパクトがあらわされている。

・Chiplets Get a Formal Standard with UCIe 1.0 Recent uptick in chiplet interest has led to concerns about lack of best practices

(4月8日付け EE Times)

→最近発表されたUniversal Chiplet Interconnect Express(UCIe) 1.0仕様は、die–to–die I/O物理層、die–to–dieプロトコル、およびPCI Express(PCIe)とCompute Express Link(CXL)業界標準を活用するソフトウェアstackモデルを対象としている。UCIeは久しぶりだといっても過言ではない。

Chipletsは新しいものではないが、最近の該テクノロジーへの関心の高まりにより、正式な標準とベストプラクティスの必要性について懸念が高まっている。

- 会社名

- Gichoビジネスコミュニケーションズ株式会社

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社

.gif)