・A New Dimension Of Complexity For IC Design 3DIC design grows more complicated

-Static timing analysis becomes more difficult in 3D(1月27日付け Semiconductor Engineering)

→3次元ICの設計には新たなレベルの複雑さが感じられる。「チップまたはチップレットを構築するときは、その中でタイミングを閉じてから、すべてがバンプを介してI / Oパッドに接続される。」とCadence Design Systemsのproduct management group director in the Custom IC & PCB Group、John Park氏。「AIB、HBI、XSRなど共通インタフェースから外れようとするなら、スペックがあり、それは別のタイプである。」

新技術、“hybrid bonding”が実装における性能を大きく切り開く、との見方である。

・Next-Gen 3D Chip/Packaging Race Begins Hybrid bonding opens up whole new level of

performance in packaging,but it’s not the only improvement

(1月31日付け Semiconductor Engineering)

→hybrid bondingと呼ばれる技術を用いる半導体の最初の波が、市場に出回っており、3Dベースの半導体製品と先端パッケージの新しい競争の時代の舞台を設定している。

最先端微細化を引っ張るインテル、TSMCそしてSamsungにおいても、さらにその先に向けて3次元IC実装を巡る競い合いが行われている、という次の状況である。

・半導体の3次元技術、インテルやTSMC火花、日本勢も商機

(2月4日付け 日経 電子版 02:00)

→半導体世界大手、米インテルや台湾積体電路製造(TSMC)などによる先端開発の風景が変わりつつある。回路の幅を小さくして集積度を高める「微細化」だけでは性能向上が追いつかず、新たな手法が求められるようになった。

各社が開発を競うのは複数のチップを積み重ねて性能を高める3次元技術。半導体技術の新たな主役が登場する中で、日本の装置や素材企業にも商機が芽生えている。

3次元ICsの課題の1つである熱の問題が話し合われている。

・Preparing For 3D-ICs Experts at the Table: The challenges of 3DICs Why disaggregation of 2D chips is so complicated, and what’s missing from the tool chain to make it easier for design teams

(2月16日付け Semiconductor Engineering)

→4人の業界専門家が3DICを巡る設計上の課題について話し合っている円卓会議。「計画に向けて早期の熱分析を行う必要があり、これには、熱の課題を解決するためのTSV(シリコン貫通ビア)が含まれる場合がある。」と、Synopsysのproduct marketing director、Kenneth Larsen氏。

3次元ICsで半導体設計が大きく転換し、半導体、パッケージ、およびボード設計と従来別々の世界の壁が外されていく、との見方である。

・3D-IC: Great Opportunities, Great Challenges 3D-ICs blur the lines between the traditionally separate worlds of chip, package, and board design

(2月17日付け Semiconductor Engineering)

→2.5Dおよび3D集積回路(3D-IC)の採用の増加は、半導体設計の世界における主要な転換点を示している。電子設計者は、AI/ML、5G/6Gネットワーク、自動運転車の増大するパフォーマンス要件を満たすために、これらの技術がシングルチップのcapabilitiesを上回っているため、より高い統合密度とより高速なデータ転送速度を求めている。3D-IC技術は、最先端の設計会社に採用され、半導体メーカーによってますますサポートされるソリューションを提供する。

3次元ICs設計での重要なポイントの1つが、あらわされている。

・Unintended Coupling Issues Grow Coupling challenges emerge with advanced IC

packaging More complex and increasingly heterogeneous designs, and multiple dies in a package, increase potential for unwanted interactions

(2月24日付け Semiconductor Engineering)

→「電子システムが複雑になるにつれて、設計によって”初めて正しく”を達成するニュアンスも高まる」とCadence Design Systemsのproduct marketing group director for system design and analysis technologiesのSherry Hess氏。「ICパッケージング技術の進歩は、優れた例であり、いくつかの課題が3DIC設計に影響を与えて、とりわけ重要なのがインタポーザなどのチップレット間の相互接続性に関連する電磁的および熱的影響である。」

先端実装での端的な利点が、以下示されている。

・Dissolving The Barriers In Multi-Substrate 3D-IC Assembly Design Ensuring the intended connectivity of the die, silicon interposer,and organic substrate

(2月24日付け Semiconductor Engineering)

→先端実装は、SoCでの従来のトランジスタスケーリングと比較して、改善されたフォームファクタ、コスト、パフォーマンス、および機能を引き続き約束する。これは、基板(有機またはシリコン)の上に複数のダイを統合することによって行われる。複数のダイに加えて、通常、3D-ICアセンブリには複数の基板が存在する可能性がある。この場合、設計者はさまざまな基板製造方法の利点を活用できるため、先端の利点はまったく新しいレベルになる。

先端実装、すなわち3次元に各社が先端切り開きに向けて入っていく理由である。

・3 Ways 3D Chip Tech Is Upending Computing AMD, Graphcore, and Intel show why the industry’s leading edge is going vertical

(3月16日付け IEEE Spectrum)

→ 高性能プロセッサの収穫は、ムーアの法則を継続するための新しい方向性がすべて上がっていることを示している。プロセッサの各世代は、前の世代よりも優れたパフォーマンスを発揮する必要がある。もっとも基本的なことは、より多くのロジックをシリコンに統合することを意味する。しかし、2つの問題がある。1つは、トランジスタとそれらが構成するロジックおよびメモリブロックを縮小する能力が低下していること。もう1つは、チップがサイズ制限に達していること。 フォトリソグラフィーツールは、約850平方ミリメートルの領域のみをパターン化できる。これは、最高級のNvidia GPUのサイズとほぼ同じである。

パワーエレクトロニクス設計での冷却技法の重要性が論じられている。

・Power Density in 3D Power Packaging Analysis: 3DIC packaging may improve IC power density Power-supply designers are more frequently being tasked to deliver higher power in the same footprint they had in their last design. 3D packaging will help make this goal a reality

(3月31日付け Electronic Design)

→Steve Taranovich氏(Freelance Technical Writer,

Phoenix Information Communication LLC)の記事。電源の設計者が、3Dパッケージング技術を使用して、次世代microchipsの電力密度を高めている。パワーエレクトロニクス設計で電力密度を上げるには、統合冷却など、今後さらに優れた冷却技法が必要になる。

先端実装の市場規模予測、および引っ張るプレイヤーの顔ぶれがあらわされている。

・Advanced packaging market to be worth 57bn euros in 2026 Yole: Advanced packaging market will grow to $60B in 2026 The advanced packaging market’s revenue is

expected to reach $57.2 billion in 2027, says Yole Developpement

(5月17日付け Electronics Weekly (UK))

→Yole Developpement社が、先端IC実装の世界市場は5年後に約$60 billionに拡大すると予測している。該市場調査会社によると、先端実装技術の上位プロバイダーは、順にASE、Amkor Technology、インテル、JCETグループ、およびTSMC。

- 会社名

- Gichoビジネスコミュニケーションズ株式会社

- 所在地

-

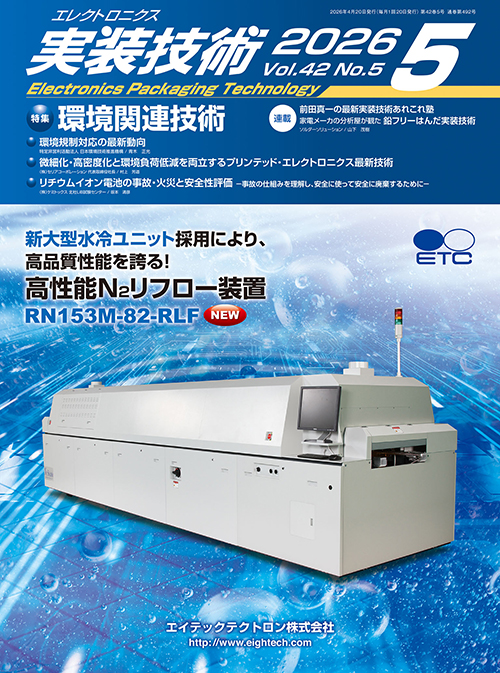

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社