3.先端実装関連の動き

引き続く激動の中、エレクトロニクス・半導体業界は、新しい要素技術、プロセス技術を駆使した新しい分野の開拓、展開が、いぜん旺盛に行われて、市場需要を大きく支えている。伸びが減速したとはいえ、大規模な世界市場を維持するスマートフォンに加えて、Internet of Things(IoT)、データセンター、自動運転車、スマートエレクトロニクスなどの新しい分野が、人工知能(artificial intelligence:AI)、深層学習(deep learning)はじめ要素技術の目覚ましい深化、高度化から市場のより大きな一角を担うようになっている。

このような状況の中、先端実装関係でも引き続き、

・新分野の高性能化、高機能化に向けた貫通電極(TSV:Through Silicon Via)、シリコンインターポーザ、チップレットなどを駆使したSystem in Package(SiP)化のアプローチ

・3D NANDに代表されるメモリ半導体での多層化による大容量化の継続進展

が前面に出て、それぞれ大きく引っ張る技術そして業界模様が続いている。Mooreの法則後の進化、展開の実現手段の大きな1つとして先端実装へ注目度が一層高まってきているこの1年の動きを、以下、次のように項目分けしてまとめる。

① 技術および市場評論

② 国際会議および展示会

③ チップレット技術関係

④ 3D NANDはじめメモリ関係

⑤ 各社・機関の取り組み

⑥ 政府・業界関連の動き

2021年10月から2022年9月までの動きについて、以下、それぞれ基本時間順に示していく。

4.技術および市場評論

2.5D、3D実装技術の進展におけるインタポーザ、チップレットなど、以下それぞれ日付け時点の見方である。

・Architecting Interposers IC interposers — a new version of printed circuit boards It’s not easy to include interposers in a design today, but as the wrinkles get ironed out, new tools, methodologies, and standards will enable it for the masses

(10月14日付け Semiconductor Engineering)

→IC設計において、インターポーザが今や、printed circuit boards(PCBs)と同様に機能し得る。「インターポーザは、異なるdiesの間で非常に大量のデータを転送するのに必要なpowerを減らすのに大方用いられる」と、Fraunhofer IISのEngineering of Adaptive Systems Division、group leader for advanced system integration and department head for efficient electronics、Andy Heinig氏。

・What’s Next For Transistors And Chiplets Imec exec discusses 3DIC packaging, chiplets, and Moore Imec’s SVP drills down into GAA FETs, interconnects, chiplets, and 3D packaging

(10月21日付け Semiconductor Engineering)

→Imecのsenior vice president of CMOS Technologies、

Sri Samavedam氏が、3DIC実装, chiplets, gate-all-

around(GAA) field-effect transistors(FETs)およびinterconnectsについて語るインタビュー記事。「Moore’s Lawの基礎である密度scalingは続いていく。」とSamavedam氏。「半導体内のトランジスタ数が年々如何に進化しているか見ていくと、Moore’s Lawにまったく密接に従っている。」

中国・JCETによる先端実装への見方である。

・A Broad Look Inside Advanced Packaging Q&A: Advanced packaging technology, trends JCET’s CTO talks about the slowdown in Moore’s Law and the growing interest in new packaging approaches and chiplets

(11月18日付け Semiconductor Engineering)

→JCETのChief Technology Officer(CTO)、Choon Lee氏が先端IC実装関連のいろいろな話題を論じるインタビュー記事。artificial intelligence(AI)、車載そして今、5Gワイヤレス技術が、次世代実装を引っ張っている。

引き続くグローバルな半導体の不足は、3次元ICで緩和できるとの見方である。

・3D-IC can ease the ongoing global chip shortage concerns:Interview with Cadence Cadence exec: 3DIC tech may resolve chip shortages(11月30日付け DIGITIMES)

→業界がmicroprocessors(MPUs)、microcontrollers(MCUs)などの半導体の供給不足に苦闘、抜け出す方法の1つに3次元デバイスのより広い採用がある、とCadence Design Systemsのsenior director、Vinay Patwardhan氏。「半導体の不足には多くの異なる理由がある。」と同氏。「純粋な技術の視点から、この適用は本当に大規模な設計を行うより優位性が得られる。」

メモリとロジックの重ね合わせへの取り組みが議論されている。

・Challenges With Stacking Memory On Logic Experts discuss stacking logic chips on top of memories Gaps in tools, more people involved, and increased customization complicate the 3D-IC design process

(12月22日付け Semiconductor Engineering)

→最新のchip-stacking技術、特にロジックがメモリの上にある3DICsについて4人の業界エキスパートが話し合うroundtable interview。「真の3D stackingについて語るとき、我々の顧客のいくつかが解決しようとしていることはまず、homogeneous stackかあるいはheterogeneous stackとしてやるかどうか、2つの層が同じ技術nodeあるいは異なるnodesにあるべきか、ということ。」と、Cadence Design Systemsのproduct management group director、Vinay Patwardhan氏。

3次元先端実装への台湾のテスト&解析各社の寄与があらわされている。

・Taiwan testing and analysis companies stand out in 3D chiplet, third-gen semiconductors

(12月29日付け DIGITIMES)

→台湾の半導体supply chainが、homogeneous/heterogeneous実装、system-level testing(SLT)、並びにmaterials analysis(MA), reliability analysis(RA)およびfault analysis(FA)向け先端技術に最大の利益をもたらす。heterogeneous integrationが、先端実装&テスト技術の牽引で重要な役割を果たす。

不足インパクトから経済安全保障の中核の1つに取り上げられ、その重要性が改めて高まった半導体の2021年が、次のようにあらわされている。

・That’s A Wrap: 3D InCites’ Top Stories and Podcast Episodes for 2021

(12月29日付け 3D InCites)

→2021年が半導体業界そして特にheterogeneous integrationにとって記念碑の年であることはいうまでもない。我々の業界は、以前決してないほど主流メディアに取り上げられ、突然に世界全体が我々の日常生活における半導体の重要性を理解している。

3次元IC設計の標準化に向けての足掛かりが探られている。

・Setting Ground Rules For 3D-IC Designs Experts discuss the details of 3DIC designs

-The few designs to reach silicon today are completely customized,with inconsistent tool

support. That has to change for this packaging approach to succeed

(1月12日付け Semiconductor Engineering)

→4人の業界専門家が3DIC設計による基本ルールの必要性について話し合っているroundtable interview。 「標準化の余地は常にあるが、該技術のこの段階ではあまり人気のないオプション」と、Cadence Design Systemsのproduct management group director、Vinay Patwardhan氏。

史上最高の半導体販売高となった2021年から、明けて迎えた2022年のはじめ時点での率直な思いがあらわされている。

・Making the Impossible Possible

(1月24日付け 3D InCites)

→1年の驚くべき成長と需要の高まりの後に、より良い未来を築く。新年は、1年先の計画を立てながら、深呼吸をし、それを保持し、過去12か月を振り返る素晴らしい時期。半導体業界では、2021年のように、多くの驚きと大きな成長が組み合わされた年は見たことがない。

3次元IC設計の高まる複雑度である。

- 会社名

- Gichoビジネスコミュニケーションズ株式会社

- 所在地

-

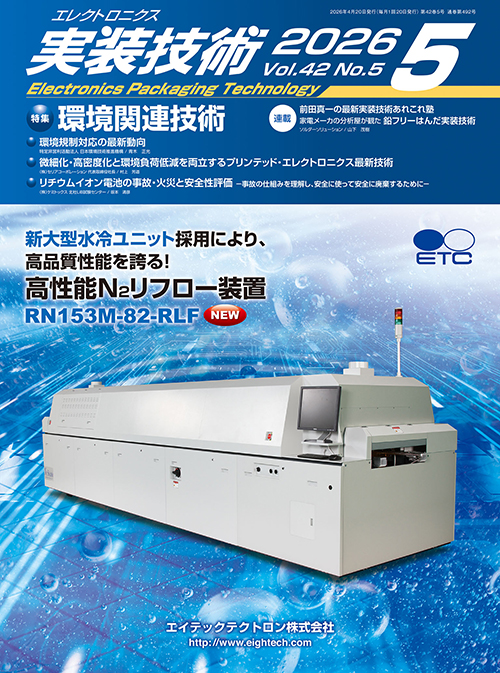

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社