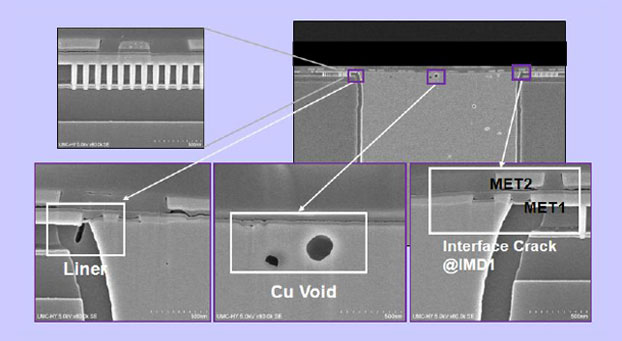

TSVの製造不良については、Hot Chips 24でのUMCの発表でも、開発初期ではいろいろなエラーが発生したものの、現在はこれらの問題は解決している、という発表もありました(図14)。

図14 TSV開発初期のトラブル(UMCのHot Cjips 24での発表資料より)

チップの3D実装に関しては、電気的な特性に関しては多くのメリットがありますが、熱は大きな問題となるといわれています。

このため、学会などでも今回紹介した以外にも多くの発表があります2)。

2.5D実装にあたっては、シリコンインタポーザはガラスエポキシインタポーザよりも熱導電率が高く、チップ面積も1チップSoCよりも多少大きくなります。このため、チップスケールパッケージ(CSP)LSIよりも多少良くなるともいわれています。

また、現在、すでに実用化がされているメモリチップの3D実装についても熱の問題は大きくありません。

これは、メモリチップのスタッキングはメモリチップの容量を増やすために行われるものだからです。いくらメモリチップを重ねても動作モードが現在の8ビットや16ビットの並列動作では、動作する回路は指定されたアドレスだけで発熱量は増えないからです。逆に、3D実装によりドライバを微小電流で駆動できるようになり、消費電流が下がります。

しかし、CPUやSoCの積層や同時に512ビットのデータをアクセスするWide I/Oメモリの積層ではパッケージの消費電力が増加し、発熱や同時スイッチングノイズの問題が解決すべき問題として大きく立ちはだかってきます。

2.5D実装やメモリチップの3D実装でTSVの普及を図りつつ、2?3年で課題を解決し、本格的なTSVを使った3D実装を立ち上げる流れが見えてきました。

日本は個々の技術はあるのですが、3D実装で何をしたいのか、何が変わるのか、トップマネジメントによるビジネスモデルが見えていないような感じがします。

iPhoneやiPadをAppleが大ヒットさせたときもそうでしたが、「何も新しい技術はない。こんなものはわが社でも簡単に作れる」というようなトップマネジメント丸出しの姿勢を打ち出すのではなく、ビジネスビジョンをもった開発を進めることを期待します。

<参考資料>

1)http://www.tel.co.jp/news/2011/1206_002.htm

2)エレクトロニクス実装学会誌 2013.Jan Electronics Packaging 2012, 1 FEM Analysis on Mechnical Stress of 2.5D Packaging Interposers Toshiya Hisada, Toyohiro Aoki, Junko Asai, Yasuharu Yamada IBM

- 会社名

- (株)日本サーキット|KEI Systems

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社