TSVによるワイドIOの現状

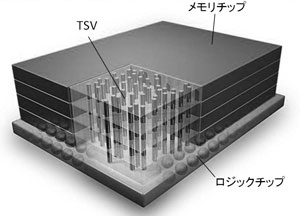

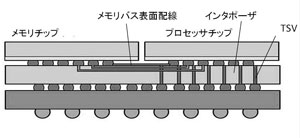

図2 TSVによるワイドIOの構造

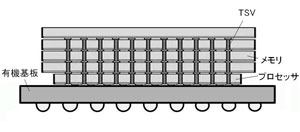

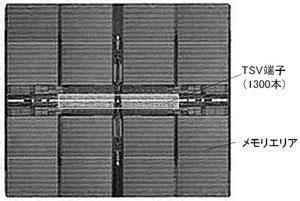

図3 ワイドIO用TSV付の4GbDRAMチップ(エルピーダ)

スマートフォン、タブレットなどのモバイル機器では動画、グラフイックスの増加、画面解像度の高精細化などで、プロセッサとDRAM間のデータ伝送速度(バンド幅)の高速化が強く要求されている。DRAMメモリの高速化にはPCではDDR(Double Data Rate)方式が採用されているが、消費電力の増加が避けられない。モバイル機器では電池の消耗が大きくなり問題となるので、低電力化したLPDDR2(バンド幅3-6GBps(ギガバイト/秒)が使われている。さらに高速化のために入出力端子数を増やしたワイドIOが提案され、TSVを使い比較的低速(200Mbps)でデータバス数を増やしバンド幅を大きくするため、メモリとプロセッサを同数のTSVで短距離で接続している。

現在目標になっているのは512ビットのバス(配線数は約1300個)で12.5GBpsのバンド幅を実現することで、その構造を図2に示す。最上層のメモリチップにはTSVは不要でフリップチップ構造になる。メモリ容量が充分ならばメモリチップが1個の場合もある。TSVの端子配置は米国のJEDEC(規格審議団体)で決定され開発が進んでいるが、2013年には実現すると期待されている。

ワイドIOの現状はメモリチップについては、エルピーダなどではすでにほぼ完成し、図3のような試作品も提供されている2)。これはメモリのチップが中央部に端子群を配置しやすいパターンになっているためと思われる。

一方、プロセッサチップのTSV化については開発に遅れが見られる。これはプロセッサの特性を保持しながらトランジスタ素子と配線の位置関係から、1300本ものTSVをチップ中央部に配置するのが難しいためと思われる。この問題を回避するためにいくつかの試みがあり、プロセッサを裏返して表面配線でメモリバスを完成させる構造(これをFace to Faceと呼んでいる)や、中間にインターポーザを挟んでプロセッサチップのTSV数を減らす提案がある。また次項に述べるような2.5D構造でプロセッサにTSVを使用しない方法も考案されているが、いずれも低電力化、コストなどの関連から更に検討が必要である。

注目される2.5D構造

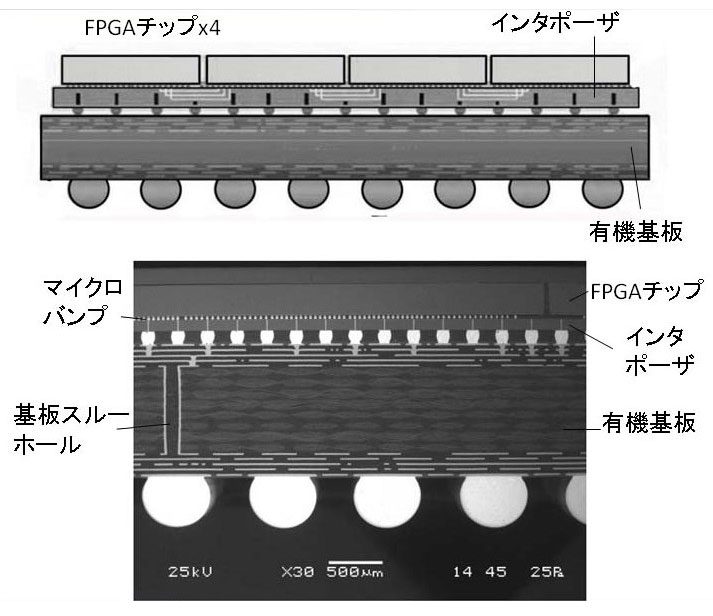

図4 Siインターポーザによる2.5D FPGA(Xilinx)

図5 2.5D構造ワイドIO概念図

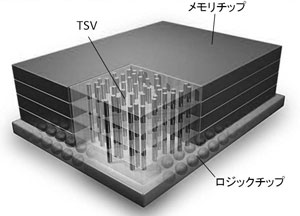

図6 ハイブリッドマイクロキューブ、2.5Dで使用(Micron)

2.5D構造とはTSVを作り込んだシリコンインタポーザ上に、TSVをもたないチップを平面的に配置したものである。TSVを使って積層したメモリスタックを載せる場合もある。インタポーザ中にはトランジスタはなくTSVと表面配線のみなので、素子を含むアクテイブチップに比べて比較的製作が容易であり、シリコン表面配線も有機基板よりはるかに微細化が可能である。2011年にXilinxが図4のように4個のFPGAチップを並べて高性能のFPGAを発表したことでにわかに注目され始めた3)。この例のように、同じチップを使う場合はホモジニアス構成と呼ばれ、これに対して別種のチップを搭載するのをヘテロジニアス構成と呼んでいる。

2.5D構造では搭載するチップはTSVなしの従来のフリップチップでよく、パッケージ高さが許せば厚いチップが使えチップの改良はほとんど不要である。インタポーザは厚いとTSVが作りにくいが、50μmでは取り扱い上、薄すぎるので、100μm程度になっている。最終パッケージをするためにインタポーザをさらに有機基板にボンディングする。この構造では各部の熱膨張係数差の問題から、5項で述べるワーページ(反り)が問題になると思われ、パッケージは金属のキャップを用いている。これらの理由から製品のコストは高くなりそうに思えるが、性能向上のメリットによって製品化が可能と思われる。

3項で述べたワイドIOの場合、プロセッサにメモリと同数のTSVを貫通する必要があるが、2.5D構造ではプロセッサにTSVの必要がないので、メモリとプロセッサを並べた2.5DワイドIOがCAEなどから提案されている4)。図5にその概念図を示す。TSVによるバスの代わりにインタポーザの表面配線で結合している。こうすると配線長は最大チップの1辺の2倍になるので1cm以上となり、TSVに等しい短距離結合はできないが、微細配線によって1300本を8mm前後の幅に収めることは不可能ではない。このバスに流れる信号は100MHzなので、電力的にはそれほど大きな負担にはならない。

消費電力が大きなファクタにはならないPC用途にはこの2.5Dが適していると考えられ、マイクロンはIBMと共同で図6のようなTSV化積層DRAMとプロセッサを有機基板上に2.5D化して、PC用やサーバ用の128GBの大容量メモリシステムをハイブリッドマイクロキューブ(HMC)として発表し5)、従来のメモリシステムに比べてサイズが10%、ビットあたりの電力も10%になったとしている。HMCは並列動作のために積層DRAMの下にロジックチップを置いていて、TSVの数や配置は不明である。またハイニックスはTSV化メモリを3Dと2.5D用に発表している。

- 会社名

- 長野実装フォーラム

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社