XJTAG社は、これらテストのライブラリを無償提供している。

このシンプルかつ洗練されたアイデアはJTAGテストへの革新となり、イノベーションとして、XJTAGを10年足らずで業界の主導的立場に押し上げることになった。『XJTAGは、より良い手法は共有するべきと考えている』

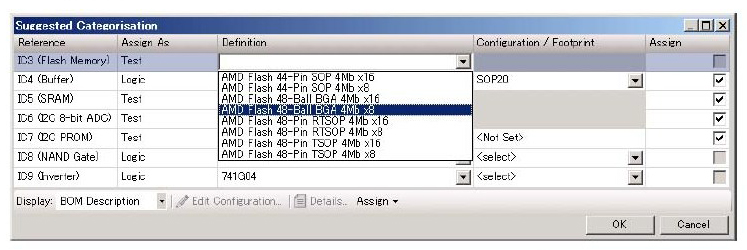

2.BOM 解析による機能テスト設定自動化

近年、電子システムの製品ライフサイクルは短くなる一方であることから、テストプログラムは容易に、かつ迅速に開発できることが求められる。XJTAGではインテリジェントなテキストベースの検索アルゴリズムによって、BOM (Bill of Materials=部品表)にあるパーツとデバイスごとのテストライブラリのマッチングを支援する。これにより基板に対する大抵のテストプログラム設定は自動化され、 設計やテストの技術者は一部の設定を追加・変更するだけで済む。そして入念に作りこまれたGUIによってテストプログラムの生産性は最大限に効率化される(図5)。

図5 デバイスごとのテストライブラリ設定をBOM解析機能で自動化支援

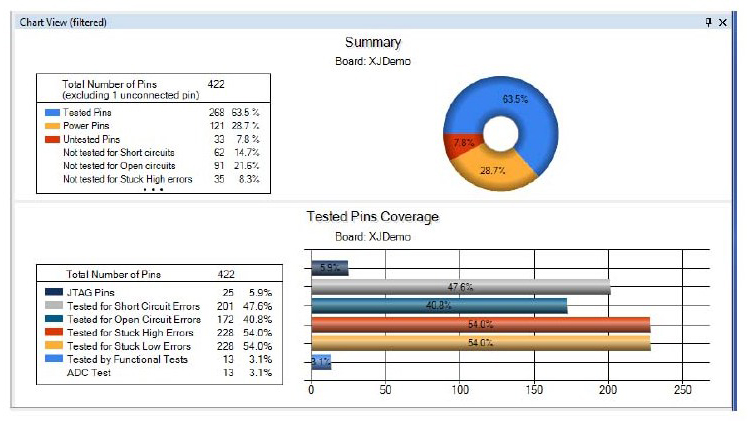

3.DFT 解析によるカバレッジから

テスト容易な設計へ改善

XJTAG社が進める設計とテスト開発の協調作業は包括的な生産性向上に寄与する。設計技術者は、DFT(Design for Test)解析機能を活用することで、従来よりも早期段階からテストを考慮に入れることができる。わずかな設計変更でテスト容易性を大きく改善することもできるし、カバレッジ結果からテストされない個所を特定することで、後の変更にかかるコストを最小限に抑えることができる(図6)。

図6 DFT解析によってテストのカバレッジを詳細に検証できる

4.テストのフォーマリズム

テストプログラム実行に影響する設計上のエラーは、クリティカルなエラーであっても設計時には見過ごされることが多い。そのようなエラーを早期に発見できることで基板の改版を削減できることが多くのユーザーから報告されている。またエラーがミッションモード動作に関わるものならばプロトタイプのデバッグ時にはチェックできない。

XJTAGには開発エンジニアが使用するシミュレータやモデリングのようなテストの手法とは違った独自のフォーマリズム(ルールや制約)があり、テストプログラムの設定を行うなかで、これを満たす必要がある。結果、有益な追加のチェックが実施される。ただ一つのエラーでも運の悪い場合にプロトタイプ基板は使い物にならないし、少なくとも対処策が見つかるまで基板の立ち上げは遅れてしまう。

JTAG信号の欠陥は事前に発見できるものの代表例であり、多くの時間と工数の軽減に貢献する。JTAG信号はプログラミングに使用されることも多く、これに欠陥があってはテストやプログラミングができない。もしJTAG信号がネットリスト上で間違って配線されているとXJTAGのテストプログラム設定ができない。

またXJTAGのテストプログラム設定時のエラー表示から、プリント配線板のフットプリントとデバイスパッケージが合わないといった致命的な欠陥を検出し、使いものにならない基板が製造されてしまう前に改善できた事例も報告されている。

『設計サイクルの早い段階で詳細を共有して様々なビューで推敲することで、XJTAGは単なるスタンドアロンのテストツールの枠を超えて、テスト項目・内容を事前に計画して視覚化できる包括的な環境を提供し、初版のプロトタイプ基板が上がるまでにテストは準備万端でデバッグを即座に開始できるようになる』。

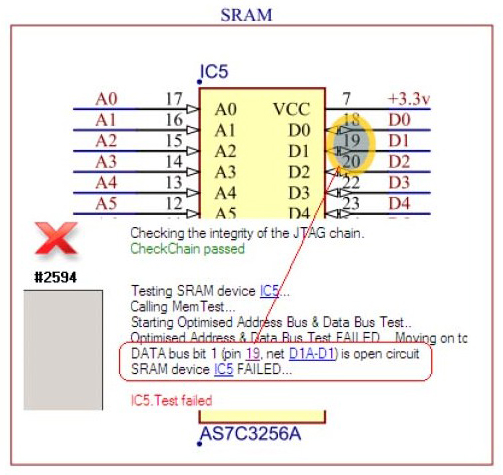

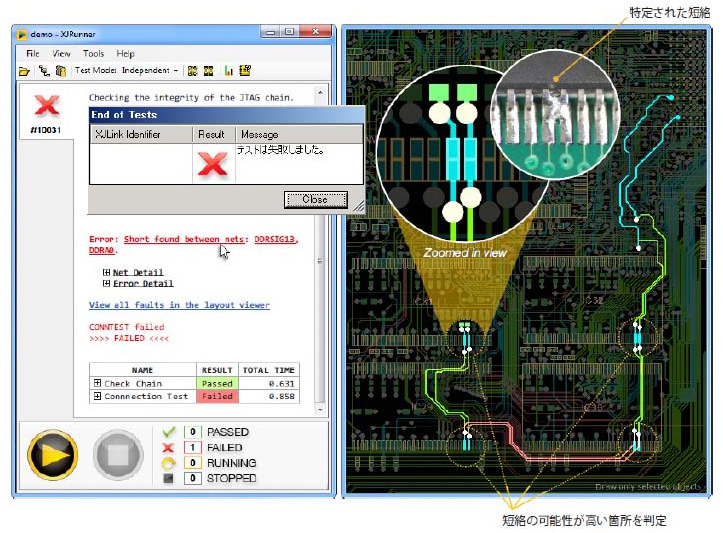

5.ランタイムデバッグ、エラー解析のビジュアル化

図7 回路図ビューアによるエラー箇所の視覚化

XJTAGバウンダリスキャンシステムのLayout Viewer機能はODB++フォーマットに対応し、基板のレイアウト情報があれば、テストネットがネットリスト上だけでなく回路図上で視覚的に確認することができる。この視覚化は製造試験時により大きな効果を発揮する。バウンダリスキャンテストでエラーが検出されれば、それに関わるネットが基板レイアウトや回路図上に視覚表示されるので、テスト担当者は該当箇所を直ちに突き止めることができる(図7)。

図8の例では、接続テストで検出された二つのネットの短絡が視覚的に特定されている。このレイアウトを見れば、DDRメモリ上の4個所のパッドがもっとも欠陥の可能性が高いことを容易に判断できる。なぜなら、同図右上のBGAデバイス部分では、これらネットのピンが隣り合っていないので可能性は低いからである。そして実際に、基板上において4個所を先に調べることで、IC31 のはんだ不良に問題があることが直ちに判明したのである。

図8 レイアウトビューアによるエラー個所の視覚化

- 会社名

- XJTAG社 / 富士設備工業(株)

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社