1. はじめに

世界スタンダードのJTAGテスト(IEEE1149.1規格 バウンダリスキャンテスト)は、高性能プロセッサ、組込み用マイコン、FPGA、PLD、DSPなどの半導体に標準で搭載されるようになった。

「JTAG(ジェイタグ)」は、一般的に開発現場で使われており、ソフトウェアエンジニアはArmマイコンのソフトウェア開発用 「JTAG ICE(デバッグプローブ)」が使われているし、ハードウェアエンジニアは「FPGAやフラッシュメモリの書き込み」のためにJTAGが使われている。

しかし、本来のJTAGの使い方は、デバッガや書き込み用のものではなく実装テスト用の標準規格である。

特にBGA部品を実装した基板においては、BGAの端子をバーチャルプローブとして使えるため、量産テストや試作基板のデバッグ、故障解析の場面で有効なテスト手法となる。

今後、DDR4メモリにはJTAGテスト用のコネクティビティテストモードが加わり、DDR5メモリはJTAGテストに対応することが決まり、JTAGテストを行う環境がさらに整うことになる。

JTAGテストの効果を企業全体で高めるには、設計段階でテスト容易化設計を考慮することが重要になる。

今回は製品のライフサイクルにおけるJTAGテストの活用例とテスト容易化設計の5つのポイントを紹介する。

2. JTAGテストの仕組み

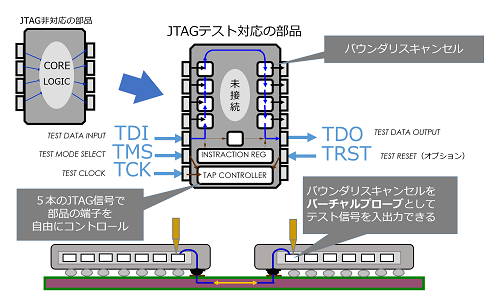

JTAGテストは、図1のように5本のJTAG信号(TDI、TDO、TMS、TCK、TRST(オプション))を利用して、JTAGテストに対応した部品をPCから自由にコントロールできる仕組みである。

図1 JTAGテストの仕組み

JTAG未対応の部品とJTAGテスト対応の部品を比較すると、部品がもつ本来のコアロジックと部品の端子の間に、バウンダリスキャンセル(Boundary Scan Cell)という信号を入出力させるためのロジックが追加されていることが分かる。

バウンダリは日本語で「境界」という意味であり、コアロジックと部品の端子の境界をスキャンできることを意味している。

このようにJTAGテストとは、バウンダリスキャンセルを制御して、部品の端子をバーチャルプローブとして通電試験ができるテスト手法である。

テスト中はJTAGテスト対応部品のコアロジックが切り離され、部品の端子から自由に信号を入出力することができる。

そのため、JTAGテストのメリットは、マイコンのプログラム開発やFPGAのロジック開発をせずに基板のテストができることである。

このテストの仕組みは、皆さまが使用している主要部品に予め内蔵しており、多ピンのFPGAやマイコンを搭載したBGA基板のデバッグ効率をあげることができる。

JTAGテストによって見つけられるBGA基板の不具合には、「はんだ不良(オープン不良、ブリッジ不良)」、「プリント基板のパターン不良(断線、ブリッジ)」、「部品内部のボンディングワイヤの断線」、「部品の型番違い」、「実装方向のミス」などがある。

JTAGテストは、測定器ではプロービングできない不良を検出できることから、近年の高密度実装基板に対する有効なテスト手法の1つとなっている。

試作基板の受入検査でJTAGテストを活用することにより、モノづくりに問題がないことを確認した上で、設計のデバッグに注力でき、開発期間を短縮できた事例もある。

また、国内では量産テストの導入事例が多くあり、JTAGテストを活用することにより、BGA実装不良品を市場に流出さない取り組みで使われている。

3. JTAGテストツール『JTAG ProVision』とCR-8000 『Design Gateway』の連携

JTAGテストの規格が誕生した1990年から約15年間は、JTAGテストツールが成熟しておらず、JTAGテストアプリケーションを準備するためには、ユーザーがテスト対象の回路図を読み解きながら、テキストエディタを使用して手作業でテストアプリケーションを作り込む必要があった。

テストアプリケーションを作るためには、回路設計者と同等に回路を理解することが求められ、JTAGテストを導入した企業では、専任の技術者を育成する必要があった。

そのため、JTAGテストを導入したものの、継続して使っていくことが困難な時代もあった。

しかし、この状況はJTAGテストツールの進化により一変した。

オランダのJTAG Technologies社が2005年にリリースしたJTAGテスト統合環境『JTAG ProVision』がリリースされ、テストアプリケーションの自動生成機能が大きく進化した。

誰でも簡単にJTAGテストアプリケーションを自動生成できるようになり、製造現場で継続して利用できる環境が整った。

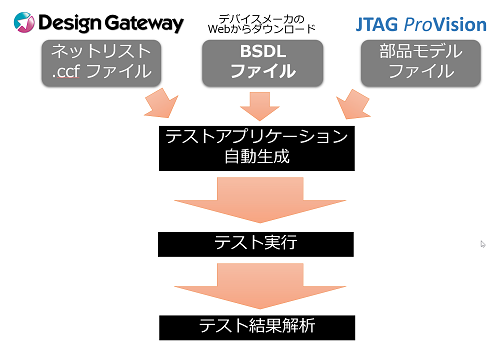

さらに図2のように、(株)図研のCR-8000『Design Gateway』の回路図CADと連携できるようになり、回路設計者の方にも使いやすく進化した。

図2 JTAG ProVisionとDesign Gatewayの連携

4.テストアプリケーション生成に必要なファイル

JTAG ProVisionを使ってJTAGテストアプリケーションを生成するためには、図3のように基板を製造するために使用するネットリスト 「.ccfファイル」(回路CAD 『Design Gateway』)から生成される配線情報)とJTAG対応部品のテスト回路情報が記載されている「BSDLファイル」(デバイスメーカーより提供されるJTAG対応部品のファイル)、JTAG非対応部品の「部品モデルファイル」(JTAG ProVisionに内蔵されている部品のロジックデータ)からテストアプリケーションが自動生成される。

図3 JTAGテスト自動生成の仕組み

BSDLファイル(Boundary Scan Description Language)とは、JTAG対応部品にどのようなバウンダリスキャン用の回路が内蔵されているか記載したものである。

このBSDLファイルには、JTAG対応部品のバウンダリスキャンセルをコントロールするための情報が記載されており、JTAGテストを実行する際には必須となる重要なファイルである。

5. JTAGテストによるBGA基板のテストカバレッジ

JTAGテストによるテストカバレッジは、JTAG ProVisionの部品モデルファイルの部品情報を元に自動生成されるため、準備されている部品モデルの種類が重要となる。

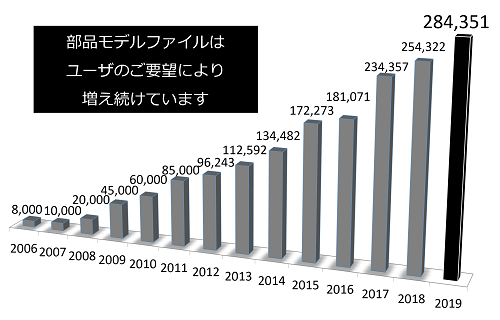

JTAG ProVisionには、図4のように2020年5月末の時点で28万種類の部品モデルファイルが用意されている。

図4 部品モデルファイルの推移

多くの場合は、製品に付属している部品モデルで十分であるが、部品モデルファイルがない場合には、メーカーで部品モデルを作成するサービスがある。

データシートのPDFファイルをメーカーに送付すると、3日ほどで新しい部品モデルファイルが提供される。

もし、機密情報が含まれる部品の場合には、ユーザーが部品モデルファイルを生成するためのツールも標準で用意されている。

この部品モデルファイルには、部品のピン情報、信号の入出力属性、出力される期待値の情報が含まれている。

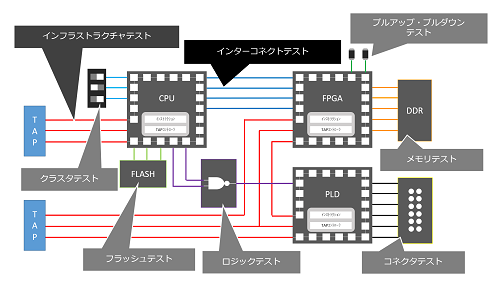

検査対象の基板に対して、どのようなテストアプリケーションが自動生成されるかを図5に示す。

図5 基板全体をテストできるJTAGテスト

「インフラストラクチャテスト」は、基板に正しく通電されているか、JTAG信号に不良がないか、正しい部品が実装されているかを、JTAG対応部品のID番号を照合してテストすることができる。

このテストに問題が無ければ、JTAGテストを実行するためのインフラが準備できたことになる。

次に実行するのは、JTAGテストのメインである「インターコネクトテスト」である。

JTAGテスト対応部品間の配線とはんだ不良の有無をテストできる。

その他のテストは、JTAGテスト非対応の部品をテストするもので、「プルアップ・プルダウンテスト」「メモリテスト」「コネクタテスト」「ロジックテスト」「フラッシュテスト」「クラスタテスト」などがある。

以前からJTAGテストを知っていた方の中には、JTAG対応部品間のインターコネクトテストしか出来ないと誤解されている方も多いようである。

現在は、JTAGテストツールの進化により、国内のお客様の事例で画像処理用の基板において、85%のテストカバレッジが得られた例もあった。

このようにJTAGテストのテストカバレッジは、劇的に向上していることが分かる。

- 会社名

- アンドールシステムサポート(株)

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社