1. はじめに

これまで、ムーアの法則を推進した原動力として、LSIパターンの微細化による集積度の向上と、デバイス構造に対して行われた数々の改善について議論してきた。最終回では、①集積度の向上は、NANDフラッシュにお任せ、②集積度より性能向上(動作速度の向上、低消費電力など)、パワーデバイスやMEMSなどを積層して新機能化を目指す“More than Moore”の動きを取り上げて、10回にわたった「ムーアの法則」のまとめとする。

2. ついに出た1Terabit(1兆ビット)メモリ

昨年サムスンが発表したところでは、「2018年には1TerabitのV-NANDフラッシュメモリを出荷し、これを1パッケージに16チップ入れた16Terabit(2TeraByte)のデータストレージを発売する」。1パッケージに16Terabitといわれると、「ムーアもびっくり」の、予想をはるかに超えた集積度である。集積度の点だけでいえば、いまやNANDフラッシュがLSIのリーディングデバイスである。もちろん、3D-NAND(3Dは3次元の意味)の老舗である東芝も負けてはおらず、QLC(Quad Level Cell : 1個のCellの信号レベルを分割して4ビットのメモリとして使う)で1.33Terabitを開発している。

その3D-NANDフラッシュは、ウエハ上にCVDで膜を多層につけ、縦にトランジスタを積む構造のため、CVD膜の層数を増やせばいくらでも集積度が上げられる画期的なアイデアである。プロセス難易度が高く、量産までに時間を要したが、現在は多くのメーカーが生産ラインを確立し、多ビット化の競争になっている。

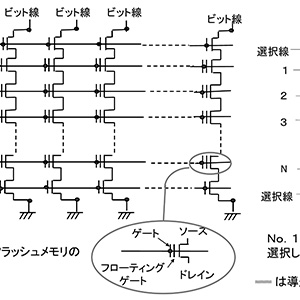

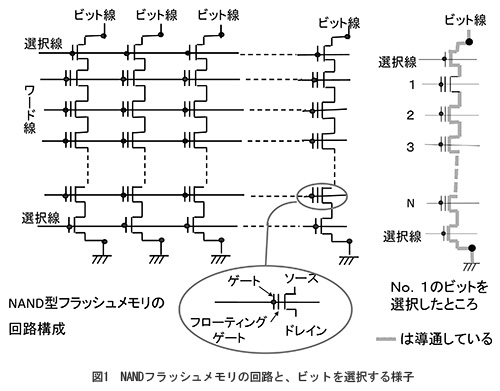

NANDフラッシュが何故集積度を増やせるのか? 図1の回路構成で説明すると、右端の太線の図は1ラインを表したもので、No.1のビットを選択する時には、他のビットをすべてON状態にする。No.1のビットのソースがビット線に繋がり、ドレインがアースに接地するので書き込みや読み出しができる。この図から明らかなように、1ビットに必要な配線は1本だけで、一般のMOSでは、電極はソース、ドレイン、ゲートの3端子で3本の配線が大きな面積を占めているのに対して、NANDフラッシュメモリは、1ビット/1本で済むため集積度の向上が簡単である。

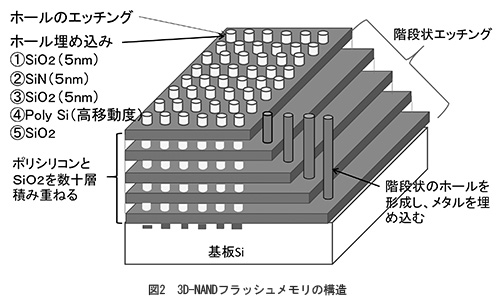

図2は3D-NANDの構造の一例で、当初はSiO2とポリシリコンのCVD膜24ペアで生産が行われたが、近く100ペアを超える層数が実現すると思われている。アスペクト比(開口と深さの比)が大きく、エッチングとCVDの技術革新が必要で、電極の取り出しも階段状のエッチングや高さの大きく異なる電極を作成しなければならず、想像を絶するほどプロセスは厄介で、これをサポートする装置メーカーが大活躍している。

以上のように、3D-NANDフラッシュは他のデバイスに圧倒的な差をつけて集積度の点での優位性は決定的である。この先も、データセンタのメモリ用など多くの需要に応えるため、集積度向上の競争は続くはずである。

3. More than Moore

2007年のITRS(ロードマップ)の会議で、ムーアの法則で集積度を上げるばかりが半導体の進歩ではない。集積度は上がらなくても、より性能が良いLSIが必要だし、センサなど異種素子を組み込んで新しい機能を発揮する素子の開発をすべきで、それを“More than Moore”と呼ぶことになった。

1. 移動度の高い異種材料の採用

前月号では、平面MOS→FinFET→水平GAA→垂直GAAと構造が代わって行く説明をしたが、構造が改善されても微細化が進むとSiの移動度が減少してしまい、駆動電流が十分に取れなくなる。そこでシリコンに代わって移動度の大きな材料を採用する研究が進んでいる。

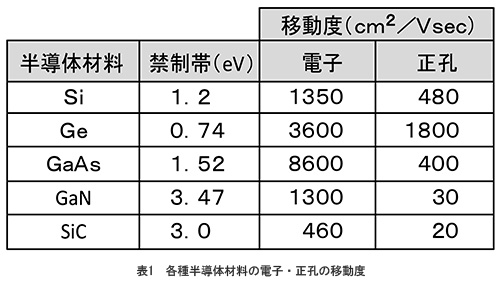

表1はいくつかの半導体の移動度を示したもので、電子(すなわちNMOSのキャリア)の移動度はGaAsの値が大きく、正孔(PMOSのキャリア)はGeが優れている。そこで、CMOS用として、NMOSにGaAs、PMOSにGeを使うのが望ましい(この表のSiCとGaNは、ワイドギャップ半導体と呼ばれてパワーデバイスの材料として期待されているので参考までに載せておいた)。

異種材料を用いる場合の最大の問題点は量産性である。Siの場合は300mm径のウエハに多数のチップが載って量産化が可能である。ところが異種材料では、そのような大直径のウエハを製作する技術がなく、量産のためにはSiウエハ上に異種材料を並べる工夫が行われている。その例を二つ上げてみる。

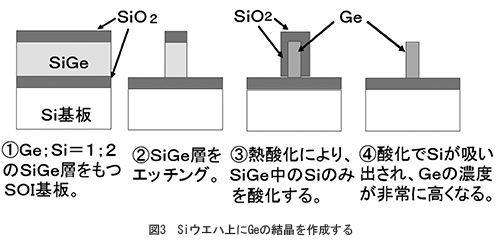

図3は、Si上にSiGeの結晶を作成し、これを熱酸化するとSiGe中のSiのみが酸化されてSiO2になり、後には酸化されないGeが単結晶として残るというアイデアで実験的には成功している。まだ、Geの結晶欠陥などがあり、実用化にはさらに検討が必要といわれている。

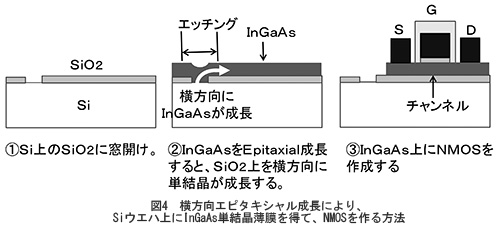

図4は、Si上のSiO2膜に窓を開けてInGaAsをエピタキシャル成長すると、SiO2膜の上を横方向に成長(Lateral Epitaxy)して薄膜の単結晶ができるというアイデアで、横方向に結晶が成長すると結晶欠陥が消滅するらしく、実験的に成功している。

これらはまだ単発の技術であって、両技術を同一のウエハ上で実現するのは容易ではなく、実際にCMOSLSIなど簡単には出来そうにない。

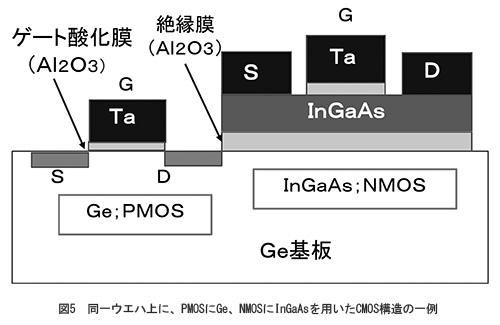

図5は、Geの結晶上でNMOSとPMOSを隣同士に作った例である。理解しやすいようにするため、元の技術発表とはやや異なった図になっている。

いずれSiは行き詰まって異種材料に移行すると思われるが、筆者の予測では異種材料CMOSが量産されるのは、早くても10年先ではないだろうか。

Geは、電子も正孔も比較的大きな移動度なので、NMOSとPMOSがともにGeで作ることも考えられ、これなら比較的早く実現するかも知れないが、300mm径のGeウエハは簡単にはできそうにないので、大量産にはかなりの工夫が必要となる。

- 会社名

- 厚木エレクトロニクス

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社