⑤半導体の進展とパッケージの進化

(1)パッケージ形態の変遷

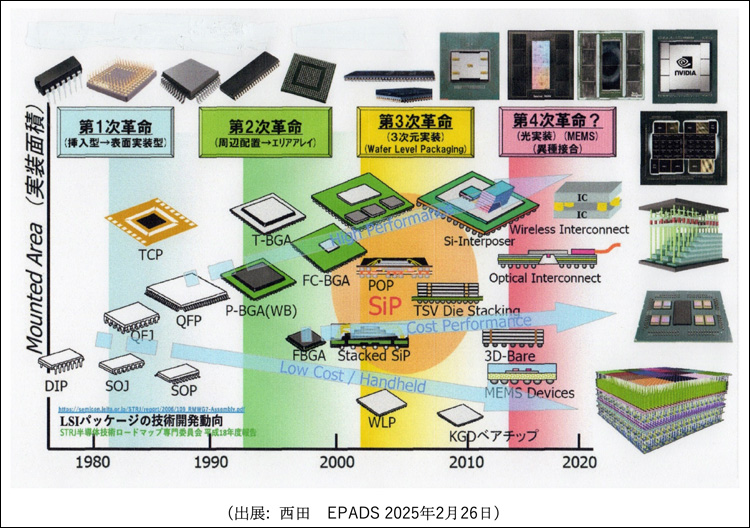

ムーアの法則に限界がみえてきた。ムーアの法則は素子を微細化することにより集積度が向上し、性能が向上、消費電力が低減、コストの低減などの効果があり、デジタル推進の原動力となってきた。しかし、チップの細線化と大型化が進み歩留まりを高めることが困難になってきた。そこで半導体の機能ごとのチップを集めてワンチップ化する「チップレット」が登場した。「チップレット」化することにより歩留まりが向上し、異なる技術のチップを1つのパッケージとすることができる(ヘテロジニアスインテグレーション)6)など画期的な方法である。チップレット方式を実現するために種々のパッケージ技術が開発されている。

図6にパッケージ形態の変遷を示す。いよいよ光電融合も視野に入ってきており、新しい時代の幕開けが始まった。現在、チップの微細化は2nmに迫っており、今後1nm以下も視野に入ってきたが、その生産には莫大な費用を要する。

図6 パッケージ形態の変遷

(2)先端パッケージ

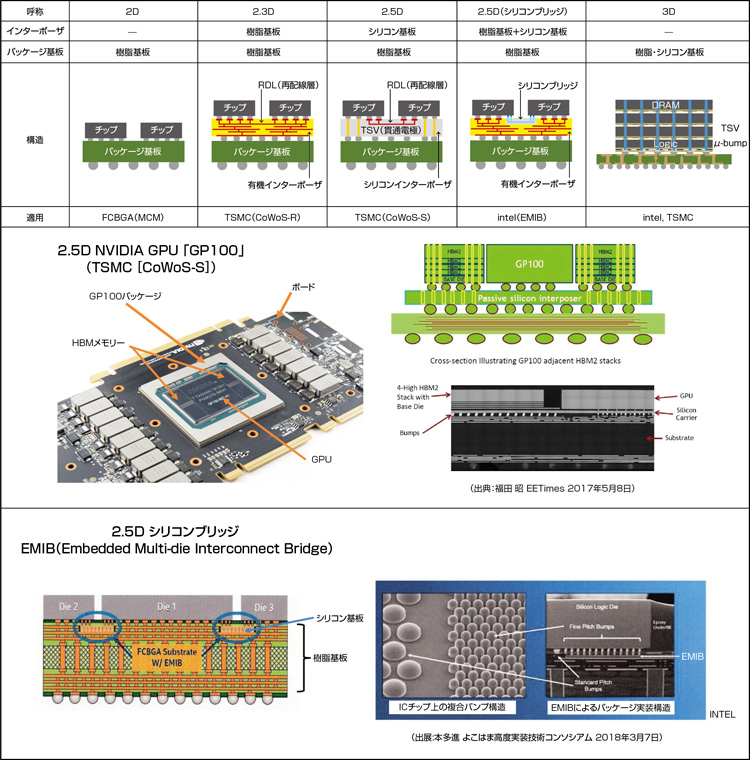

図7に2D 、2.3D、2.5D、3Dのパッケージ構造を示す。2Dは従来からのMCM(マルチ ・ チップ ・ モジュール)でFCBGAと呼ばれている。

図7 2D~3Dパッケージ

2.3D実装は、パッケージ基板(サブストレイト)とICとの間に有機インターポーザを配した構造になっている。樹脂基板はシリコンインターポーザと較べてその製造コストを抑えることができるので、PCやタブレットその他の機器に使用されている。今後、樹脂基板の配線がシリコンの微細配線にどのくらい近づけられるかは興味深い(図3(P38)参照)。有機材料はシリコンより誘電率が低く電気特性に優れている。

2.5D実装は、パッケージ基板とICの間にシリコンインターポーザを配した構造になっている。加工はウエハ工程を使用するので高密度配線の微細加工が可能である。シリコンインターポーザは非常に高価なのでAIやHPC(ハイパーフォマンス ・ コンピューティング)の用途にしか使えない。シリコンインターポーザの基板は300mmφのウエハから切り出すので取れ数が限られる。

近年、シリコンはコストが高額なのでガラス基板が注目されている。ガラス基板の大きさは510×515mmで、シリコンの300mmφより取れ数が多い。しかしその生産には多くの問題を抱えているが量産へ向けて開発が進んでいる。またガラスはシリコンより電気特性(誘電率)が優れている。

2.5Dシリコンブリッジは有機基板に部分的にシリコン基板を埋め込み、シリコン基板部でICどうしを接続する。この方法は高価なシリコン基材の使用量を大幅に減らせる効果があり、すでに実用化されている。しかし、位置合わせなど、技術的に難しい問題がある。

3D実装は、複数のチップをTSVに使用して垂直に積層する3次元構造で、究極の実装を実現する技術である。

図7に2.5D実装のNVIDIA半導体GPUのGP100を示す。GP100パッケージには、GPU100プロセッサと積層されたHBMメモリーが4個搭載されており、シリコンインターポーザを使用しパッケージの大きさは29×40mmと巨大である。最新のNVIDIAのGPUはさらに巨大化している。

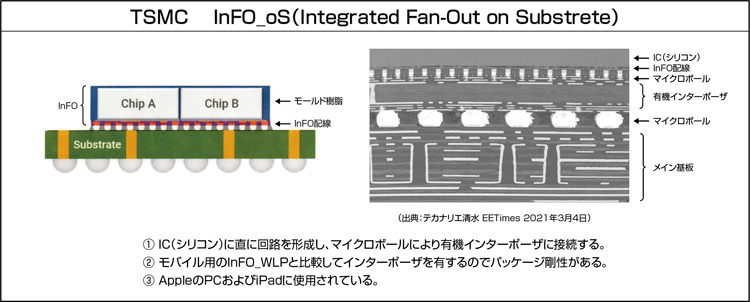

図8にTSMCのInFO_oS(Integrated Fan-Out on Substrate)パッケージを示す。TSMCはAIや高性能コンピューティング(HPC)向けに2.5D実装シリコンインターポーザ(TSMCの呼び名 : CoWoS_S)を製造している。しかしそのパッケージはあまりにも高額なのでTSMCはモバイル向けに低価格のパッケージInFO_oS(Integrated Fan-Out)を開発した。InFO_oSはInFO構造のLSIにインターポーザを付加した構造で剛性を確保している。InFO_oSはAppleのPCとiPADに使用されている。

図8 InFO_oSパッケージ

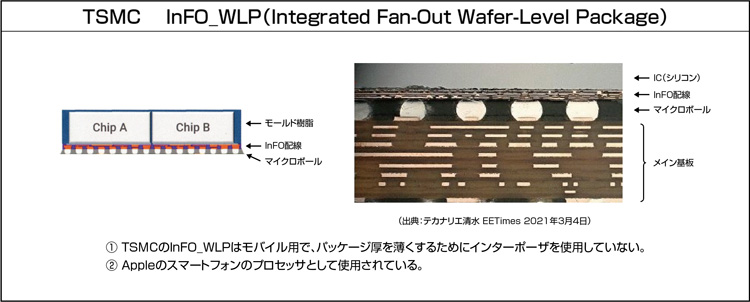

図9にInFO_WLPの構造を示す。InFO_WLPはモバイル用で、その実装厚さを薄くするためにパッケージ基板を使用していない。このパッケージはAppleのスマートフォンのアプリケーションプロセッサに使用されている(写真3(P39) AppleA11参照)。

図9 InFO_ WLPパッケージ

InFO_WLPはTSMC社の呼称で、一般的にはFO_WLP (Fan-out Wafer Level Package)と呼ばれ、Infineonが2006年に開発したeWLB技術が元になっている。FO_WLPはICをモールド材で固定し、IC表面とモールド材のファンアウト部に再配線層 (RDL)を設け、出力側にはんだボールを搭載する構造になっている。再配線層は、感光性のポリイミド樹脂と配線にはスパッタ下地の銅めっきが使用され、薄い膜厚の再配線層を形成している7)、8)、9)、10)。

(3) SAP工法とEFM社の精密<縦型現像機>

第4章にスマートフォンのメイン基板の細線化にともないMSAP工法が採用され、DFRの現像機が水平型現像機から<縦型現像機>に移行したことを記述した。

高機能のパッケージ基板ではさらなる細線化が進んでおり、SAP工法により20〜10μピッチの製品が上市されており、今後10μピッチ以下も計画されている。SAP用にはMSAPよりさらなる極細線に対応した精密<縦型現像機>が必要になる。

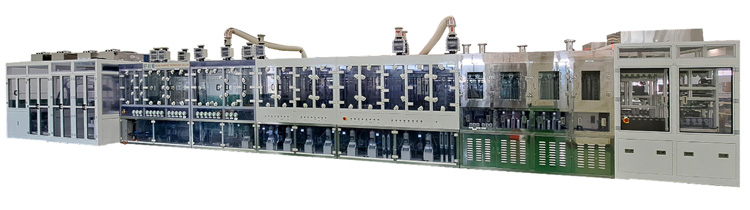

台湾のEFM(ECLAT FOREVER MACHINERY CO., LTD)社は、SAP対応の精密<縦型現像機>を発売している。写真6にEFM社の<縦型現像機>の全景を示す11)。

写真6 EFM社の精密<縦型現像機>

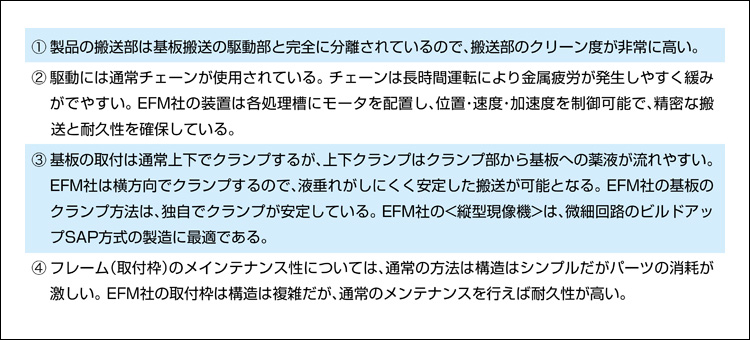

EFM社の<縦型現像機>は特にパーティクル対策に力を入れており、種々の対策によって配線のファイン化に対応している。その構造は、搬送部と駆動部を完全に分離し、搬送部を気密化してパーティクルの侵入を防いでおり、駆動部のギア部分もパーティクルの発生を抑える構造になっている。処理槽(基板搬送部)はパーティクルの侵入を防ぐために二重にして気密性を向上させている。EFM社の<縦型現像機>は、プリント基板をフレーム(基板枠)への取り付け方法がユニークで、クランプは縦方向ではなく横方向でクランプして薬液の垂れの影響を無くしている。またクランプはクランプする力を変更できる精密な構造になっている。EFM社の<縦型現像機>の特徴を図10に示す。

図10 EFM社の縦型現像機の特徴

(4)0.1mmガラス基板への挑戦

EFM社は、昨年、0.1mm厚ガラス基板を<縦型現像機>で流動させることに成功した。ガラス基板搬送のために基板のクランプ方法や各処理槽での処理方法を改良することにより搬送でのガラス基板の損傷を無くした。写真7にノギスによるガラス厚の測定を示す。

写真7 ガラス厚0.1mmの測定

<参考文献>

1)日経エレクトロニクス

「iPhoneXの基板は2階建て 予想外の方法で接続」

2017年12月 pp.26-27

2)日経エレクトロニクス

「iPhoneⅩ徹底分析 判明した4つの予想外」

2018年1月 pp.100-106

3)日経エレクトロニクス

「分解写真で見る新型iPHone 巨大フレキと2階建て基板に得心」 2019年12月 pp.73-82

4)上田弘孝

SemiConsult「2大スマートフォンメーカーのスマホ最新実装技術」

2018年6月 2018エレクトロニクス実装学会

最先端実装技術技術シンポジュウム

5)日経クロステック

「iPhone16 Pro Maxの徹底分析」

2024年12月19日

6)日経クロステック

「半導体微細化終焉に新シナリオ、技術限ではなく需要の減退」

2022年8月18日

7)前田真一/本多進

「次世代配線板の狙うべき方向と課題」

エレクトロニクス実装学会誌 Vol.1 No.1 MAY 2018

8)栗田洋一郎/システムインテグレーション実装技術委員会

「チップレット集積技術の現状と最新動向」

エレクトロニクス実装学会誌 Vol.26 No.1 Jan 2023

pp.19-27

9)西田秀行/システムインテグレーション実装技術委員会

「システムインテグレーション実装技術の現状と展望」

Vol.27 No.1 Jan 2024 pp.59-70

10)馬場伸治/ルネサスエレクトロニクス株式会社

「チップレットとは何か」 2024年10月4日 C-NET月例研究会

11)電子デバイス産業新聞

「EFM社のCEOインタビュー」

2025年3月6日

敍豐企業股份有限公司

Eclat Forever Machinery Co., Ltd.

営業担当 周雨農

Tel: 886-3-3646445 ext.124

Fax: 886-3-3674060

Taiwan cellphone +886933980479

- 会社名

- 特定非営利活動法人 サーキットネットワーク

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社