デカップリング用コンデンサの静電容量設計

1.情報用電子機器の機能回路ブロック構成例とデカップリング用コンデンサ使用回路例

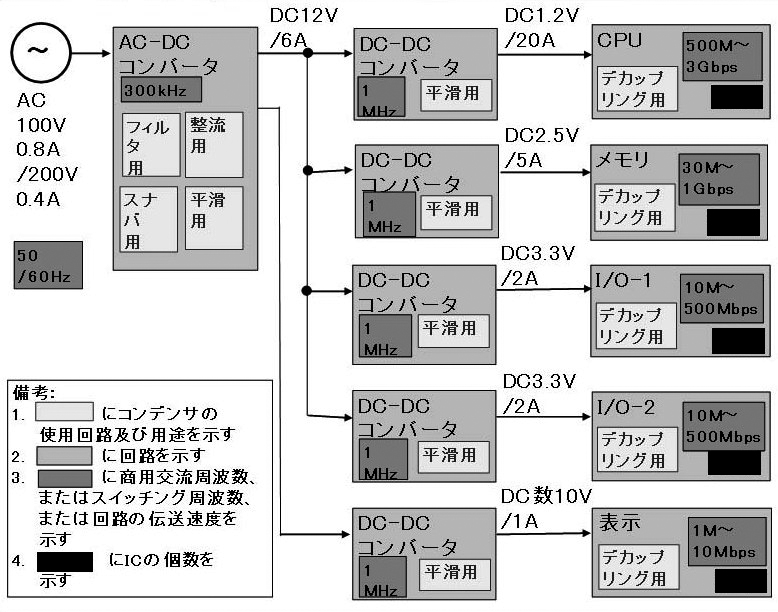

デカップリング用コンデンサが使用される代表的な電子機器は情報用電子機器である。図2に情報用電子機器の機能回路ブロック構成例とコンデンサの使用回路用途例を示す。ここで、情報用電子機器の機能回路ブロック構成例は業務用情報端末機器の例によっている。また、デカップリング用コンデンサ使用回路例はコンデンサの使用回路用途例の中に示す。

図2 情報用電子機器の機能回路ブロック構成例とコンデンサの使用回路及び用途

2.デカップリング用コンデンサの静電容量設計例

(1)電源側デカップリング用コンデンサの静電容量設計例

電源側デカップリング用コンデンサの設計静電容量を算定する。

①CPU

電源側デカップリング用コンデンサの充電または放電電荷量ΔQは

ΔQ=電流×1充電または放電時間×5=20×2×10−9×5=200×10−9 [C]

容量CDBの電荷量にΔQの変化が生じたとき変化する両端の電圧ΔVDBは

ΔVDB = ΔQ /CDB

電圧変動を1%以内に抑えるためのCDBは

CDB=(200×10−9)/(1.2 ×0.01)=17×10−6 [F]=17[μF]

②メモリ

電源側デカップリング用コンデンサの充電または放電電荷量ΔQは

ΔQ=電流×1充電または放電時間×5=5×33×10−9×5=825×10−9 [C]

電圧変動を1%以内に抑えるためのCDBは

CDB=(825×10−9)/(2.5×0.01)=33×10−6 [F]=33[μF]

③I/O-1/2

電源側デカップリング用コンデンサの充電または放電電荷量ΔQ は

ΔQ=電流×1充電または放電時間×5=2×100×10−9×5=1000×10−9 [C]

電圧変動を1%以内に抑えるためのCDBは

CDS=(1000×10−9)/(3.3×0.01)=30×10−6[F]=30[μF]

④表示

全IC側デカップリング用コンデンサの充電または放電電荷量ΔQは

ΔQ=電流×1充電または放電時間×5=1×1000×10−9×5=5000×10−9 [C]

電圧変動を1%以内に抑えるためのCDBは

CDS=(5000×10−9)/(50×0.01)=10×10−6 [F]=10[μF]

(2)IC側デカップリング用コンデンサの静電容量設計例

IC側デカップリング用コンデンサの設計静電容量を算定する。

①CPU

IC側デカップリング用コンデンサの充電または放電電荷量ΔQは

ΔQ=1ICの電流×1充電または放電時間=(20/4)×2×10−9=10×10−9 [C]

電圧変動を±1%以内に抑えるためのCDSは

CDS=(10×10−9)/(1.2×0.01)=0.83×10−6[F]=0.83 [μF]

②メモリ

IC側デカップリング用コンデンサの充電または放電電荷量ΔQは

ΔQ=1ICの電流×1充電または放電時間 =(5/4)×33×10−9=41×10−9[C]

CDS=(41×10−9)/(2.5×0.01)=1.6×10−6 [F]=1.6[μF]

③I/O-1/2

IC側デカップリング用コンデンサの充電または放電電荷量ΔQは

ΔQ=1ICの電流×1充電サイクル時間=(2/2)×100×10−9=100×10−9[C]

電圧変動を1%以内に抑えるためのCDSは

CDS=(100×10−9)/(3.3×0.01)=3.0×10−6[F]=3.0[μF]

④表示

IC側デカップリング用コンデンサの充電電荷ΔQは

ΔQ=1ICの電流×1充電または放電サイクル時間=(1/2)×1000×10−9=500×10−9 [C]

電圧変動を±1%以内に抑えるためのCDSは

CDS=(500×10−9)/(50×0.01)=1.0×10−6 [F]=1.0[μF]

- 会社名

- (有)イー・コンポーネンツ

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社