1. はじめに

昨年は、JAXA、鉄道総研、JAMSTECと、エレクトロニクスと直接的には関係の薄い研究所を取り上げたので、本年はエレクトロニクス関連の研究所を紹介することにする。

その第1回として、NHK放送技術研究所(以下、NHK技研と略称する)を取材させていただいた。

2. NHK技研の概要

NHK技研は、日本でラジオ放送が始まった5年後の1930年に設立され、放送技術全般にわたる日本で唯一の研究所として、放送の進歩発達に関わる調査・研究を基礎から応用まで一貫して取り組んできた。

1966年には衛星放送の研究が開始され、1984年には試験放送が始まった。

スーパーハイビジョンは、1995年に研究を開始され、昨年放送が開始された。

これまでの経験では、一つのシステムが完成し実用化されるのに約20年かかっている。

したがって、現在は20年後の社会情勢などを考慮しながら、次のような研究テーマを設定している。

インターネットのサービス、次世代テレビ方式、AI(人工知能)、空間表現(3次元、AR、多視点カメラなど)、新機能デバイスなど。約230名の研究員である。

ご報告したい話題は豊富にあるが、今月は撮像デバイスを取り上げることにする。

3. イメージセンサの解説

CMOSイメージセンサは、スチルカメラやスマートフォンに大量に使用され、多くの皆さんに愛用されている。

イメージセンサの構造や動作を十分ご存知の方も多いと思われるが、念のため筆者の分かる範囲で一般的な解説をしておく。

レンズを通った光はイメージセンサに入り、光の強度に応じた量の電子(または正孔)を発生する原理を使っている。

古くは入射光量によって導電率が変わる酸化鉛のプランビコンや硫化アンチモンのビジコン撮像管が放送に使われていたが、シリコンのCCD(Charge Coupled Device)の登場によりシリコンに置き換わっていった。

太陽光発電は、半導体のPN接合で光を電気に変換するものであるが、イメージセンサも同じ原理で光を電気に変換する。

太陽光発電には色々な材料が使われているが、イメージセンサではシリコンが多く使用される。

シリコンは、LSIでプロセス技術が完成しているという以外に、可視光域をカバーできる点が重要である。

NHK技研では、シリコンでは満足しないで、より感度のある材料の研究もされている。

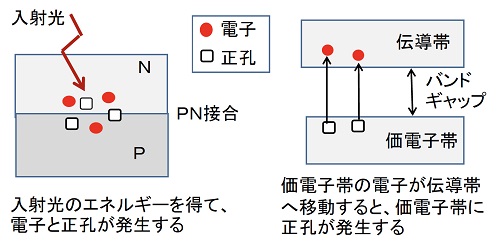

図1は、シリコンのPN接合に光が入射した時の説明である。

図1 半導体に光が入射すると、電子と正孔が発生する

光(フォトン)のエネルギーで結晶格子に捕まっていた電子が飛び出して、電子と正孔がキャリアとなる。

ただし波長が1μ以上の赤外線は、シリコンのバンドギャップを飛び越すエネルギーが不足で電子と正孔は発生せず感度がない。

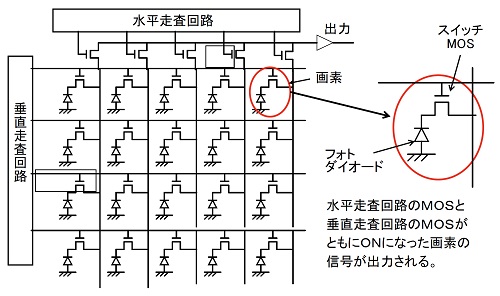

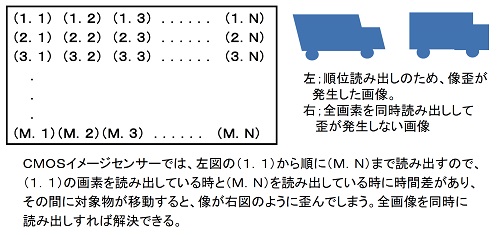

イメージセンサは、数百万以上の画素ならなっているが、それぞれの画素で入射光に応じた電子が発生し、図2のように水平走査回路と垂直走査回路で、端の画素から順にONになった画素の信号が出力部へ送られ読み出される。

図2 CMOSイメージセンサの構造

図2から分かるように、各画素は長い配線などに接続しているので、ノイズを拾ってしまう。

イメージセンサの感度を上げるには、回路で増幅すれば良いが、ノイズがのっているとノイズも一緒に増幅されて見苦しい画となってしまう。

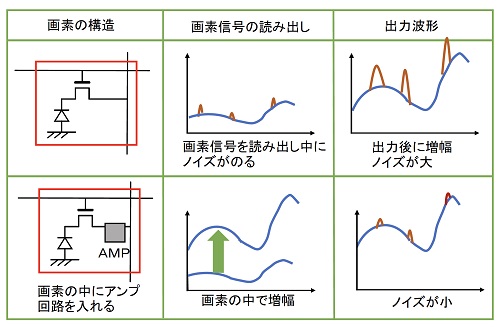

そこで、各画素の中に増幅回路を組み込んで、ノイズが入らない内に増幅してしまう構造が開発され、感度が大幅に向上しCMOSセンサが実用化された(図3)。

図3 各画素にアンプを組み込むことにより、ノイズの少ない信号が得られる

小さな面積の画素内に増幅回路を入れると、光を受ける面積が少なくなってしまうが、LSIの微細化技術の進歩により、増幅回路が入れられるようになった。

4. 3次元構造撮像デバイスの開発

NHK技研では、超多画素と高フレームレートを両立する次世代のイメージセンサの実現を目指して、3次元構造撮像デバイスの研究を進めている。

イメージセンサの3次元化では、TSV(Through Silicon Via)を用いた構造が実用化されているが、TSVでは数ミクロン以上の面積が必要となり、画素毎の対応はできない。

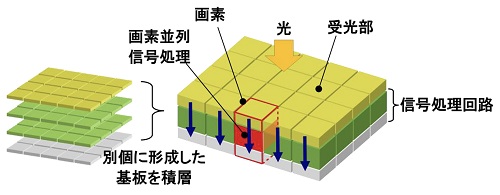

NHK技研で開発に取り組んでいるデバイスは、異なる基板に形成した受光部や信号処理回路を接合して、受光部直下に画素毎に信号処理回路を集積した構造を備えている(図4)。

図4 3次元構造撮像デバイス

上下の基板の接続には、微細な金電極を上下に設けて超平坦化を行い、金と金の圧着を行う。

これにより、全画素並列に信号処理を行うことで、多画素でも高いフレームレートを維持することができ、高機能化も可能である。

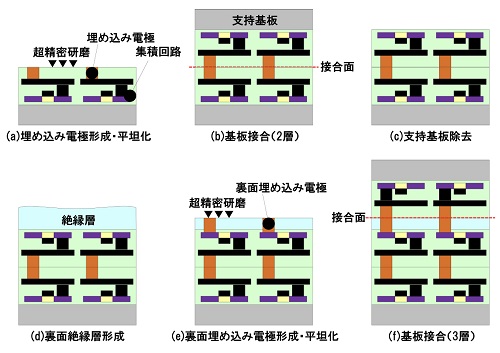

これまで、デバイスの高集積化に向けて、3層以上の構造を実現する多層化プロセスを開発した(図5)。

図5 多層化プロセス

試料の作製手順は、シリコンIC基板にアルミニウム配線を行い、絶縁膜(SiO2)を被せて所定の孔を開けて、金をめっきする。

さらにCMP(Chemical Mechanical Polish)で平坦化する。

貼り合わせる方の基板も同様な構造にしてチップを切り出し、金を対向させ、荷重2000N、温度200℃、60分間加圧して接合させる。

2層構造を形成する技術(図5(a)~図5(c))に加えて、新たに集積回路の裏面に絶縁層と埋め込み電極を形成する技術と、裏面側の平坦化技術(図5(d)~図5(e))の開発により、3層構造デバイスの試作に成功した。

本プロセスの繰り返しにより、さらなる多層化の実現性が高まり、従来平面状に形成してきた信号処理回路を3次元構造化することで、画素サイズの縮小と信号処理回路の高集積化の両立に向けた見通しを得た。

この技術により、将来的には超多画素でも高フレームレートやグローバルシャッターが実現される(グローバルシャッターの説明は図6に示した)。

図6 順次読み出しによる像歪を解決する同時読み出し。これをグローバルシャッターと呼んでいる

- 会社名

- 厚木エレクトロニクス

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社

.gif)