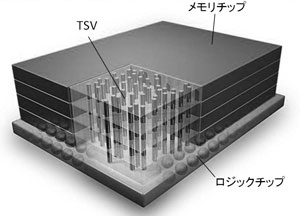

実用化が進み始めたTSV採用デバイス

シリコンチップ内にビアを作成したシリコン貫通電極(Through Silicon Via、以下TSV)によって半導体を3次元的(以下、3D)に積み重ねて高密度デバイスを作るTSV技術は、半導体の微細加工の限界を超えるための次世代の新技術として注目され、10年近くにわたって活発に研究開発が続けられ、試作品は数多く発表されたが、実用的な量産品としては成功しなかった。その理由は加工工程の増加によってコストが上昇し、技術的難度によって歩留りも低下するためで、TSVによる高性能化と小型化のメリットがコスト上昇に見合わなかったためといえる。

しかし昨年からこの状況が変わりつつあり、TSVの実用化デバイスの発表が増えてきた。そのひとつとして、スマートフォンなどのモバイル機器用のDRAMメモリの高速化の要求に対して、プロセッサとの信号伝送用のバス幅を増加させて低電力化させた、TSVによるワイドI/O構造が注目されている。ワイドI/Oメモリはスマートフォンの爆発的な増加から、TSVに対するキラーアプリ(大きな需要が期待できる応用)として考えられ、世界の半導体メーカーが開発を進めている。

また、TSVをもつシリコンインタポーザを使った2.5次元(以下、2.5D)デバイスは3D構造より比較的製作が容易とされ、高価格でも性能のよいFPGA(現場プログラムの可能なLSI)などが評価され始めた。またTSVの製造工程、装置、材料は過去に多くの種類が検討されてきたが、最近になってほぼ標準と考えられる工程が固まってきたので、これらについて述べる。

ビアミドルとビアラスト

TSVは半導体の製造工程中で作られるが、半導体製造は大別するとトランジスタを作るFEOL(Front End of Line)、回路配線を作るBEOL(Back End of Line)、パッケージに組み込む実装工程(後工程)に分けられ、ビアをウエハ表面から作るか、裏面から作るかの選択もあり、従来5種類の製作ポイントが提案されていた。しかし最近はビアミドル(FEOLとBEOLの中間点で表面から)とビアラスト(実装工程前に裏面から)の2種類に絞られてきた。

最近半導体の製造の流れ(サプライチェン)が従来の半導体メーカーによる一貫工程からファウンドリ(前工程専門メーカー)とOSAT(Outsourced Semiconductor Assembly and Test、後工程専門メーカー)に分けられつつあることから、ビアミドルはファウンドリ、ビアラストはOSATに適しているともいわれている。

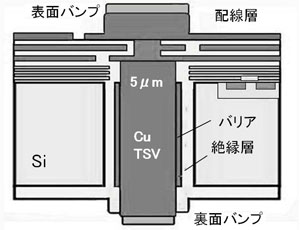

代表的なビアミドルの断面図を図1(a)に示す。ボッシュプロセスと呼ばれる異方性と等方性のイオンエッチングを繰りかえしてシリコンにビアを開孔し、絶縁用のシリコン酸化膜と銅のバリアとなる膜を生成させ、めっきにより銅を充填する。ビアのサイズは用途によって異なるが、最近のメモリ用などの標準としては深さ50μm(すなわちチップの厚さ)、直径は5μm程度である。ビアラストによるTSVの製作法はビアミドルとかなり異なるが、結果としての断面はよく似ている。ビアの製作については多くの技術開発が関連するが、詳細については誌面の都合で省略する。

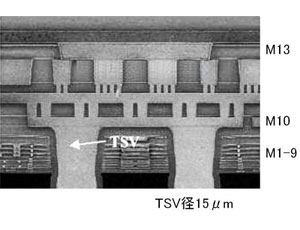

ビアミドル、ビアラストともにいくつかの課題をもっていて、関連する論文も数多く発表されている。TSVのビアを配線層中のどの配線に接続するかは、従来あまり議論されなかったが、IBMの発表では、図1(b)のように十数層ある配線の最上部に近い厚い配線に接続されている1)。図中Mは配線層を示す。下層の薄く微細な配線への接続は難しいと想像され、回路的にも外部端子に近いことから当然である。

図1 ビアミドルTSVの構造:(a)Cu-TSV断面

図1 ビアミドルTSVの構造:(b)上層配線とビアの接続

ビアミドルではビア内のめっきされた銅が、その後の熱処理で膨張して銅配線を切断するポンピングまたはProtrusion(膨張)現象が観測され、これを防ぐためにめっき後の適当なアニーリング処理が必要であることが判ってきた。またビアの深さの精度が悪いとウエハ薄化後の裏面バンプの高さがばらつき、ボンディング歩留まりを悪化させる。ビアラストではウエハのサポート接着剤の耐高温性や低温での酸化膜生成が必要になり、またイオンエッチングがビア底部で配線までを切断しないような、エッチングストップ材料の選定やエッチングの加工精度の向上が必要である。

- 会社名

- 長野実装フォーラム

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社