6. HALT試験装置とJTAGテストの結合テスト

今回、JTAGテストシステム『JTAG ProVision』と結合したHALT試験装置『Typhoonシリーズ』は、HALT試験装置の代表的な製品で、製品開発プロセスの初期段階でHALTを実施することで、製品の信頼性を高めることができる(図9)。

図9 JTAGテストとHALT/HASS試験装置

またHASS(Highly Accelerated Stress Screen)にも対応しており、HALTで得られた限界試験データを元に、量産品の製造工程での変化やばらつき、潜在的不具合がないかを監視するためのスクリーニングをすることができる。

お客様の製品サイズや数量、重量に合わせた試験機があり、テーブルサイズは457×457mm~2540×1219mm、テーブル最大積載重量は36~544kgまで対応している。

最大加速度75Grmsの6自由度振動と-100℃~250℃の広温度範囲、70~100℃/minの急速な温度変化を実現できる。

また、効率的な気流特性とテーブル位置を変更できる構造で、液体窒素や電力コストを削減することができる。

今回は、ザイリンクス社のFPGA(BGAパッケージ、196ピン)を搭載した基板で信頼性評価を行った。

HALT試験装置への基板固定方法は、図10のようにアルミフレームに4隅で固定した。

.jpg)

図10 HALT試験装置への基板固定方法

HALTでは、基本的に治具設計基準として加速度については、テーブル制御加速度≦試料加速度という基準で設計をする。

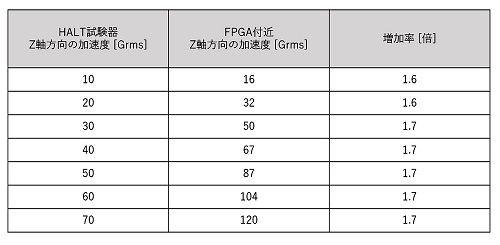

試料加速度の確認のため、FPGA付近のZ軸方向の加速度を測定したところ、図11のような相関関係を確認できた。

図11 FPGA付近の加速度

短時間で信頼性評価を行うために、HALT試験装置の加速度を70 [Grms]に設定し、FPGA付近の加速度を120 [Grms]として試験を行うことにした。

試験条件は、温度条件を設定せずに常温とし、HALT振動試験の合計時間は100分、HALT試験装置の加速度を70 [Grms]と設定し、5分間実行と1~2分間停止を20回繰り返した。

JTAGテストのサンプリング時間は30秒として、HALT振動試験を行っている100分間連続実行して、FPGAのピンをバーチャルプローブとしてBGA部品のはんだ接合状態をスキャンした。

7. HALT試験の結果(スタティック状態)

HALT振動試験を5分間実行と1~2分間停止を繰り返し行い、振動を停止した状態(スタティック状態)でJTAGテストを行った結果を図12に示す。

.jpg)

図12 HALT試験の結果(Static状態)

図中の白丸は、BGAのピン配列を示していて、A1ピンからP14ピンまでの196ピンのBGAパッケージのはんだ信頼性試験を行った。

今回は、50分経過後から10分間隔の試験結果を紹介する。

開始から50分経過したところで、左上のB1ピンでオープン不良が検出され、60分を経過したあたりから右上のA12ピン、B14ピンのオープン不良が現れた。

90分が経過すると、左下のM1ピンとP4ピンにオープン不良が現れるようになった。

BGA部品に振動を与えて、振動を止めた状態でJTAGテストにより電気試験を行っている。

そのため、振動が止まったタイミングでBGAのボールと基板のパッドが浮いたときに不良が検出され、はんだが剥離してもボールと基板が接触しているときには、不良が検出されていないことがわかる。

8. HALT試験の結果 (ダイナミック状態)

HALT振動試験を5分間実行と1~2分間停止を繰り返し行い、スタティック状態と同様にダイナミック状態(振動中)においても、JTAGテストでBGAはんだ状態を測定した。

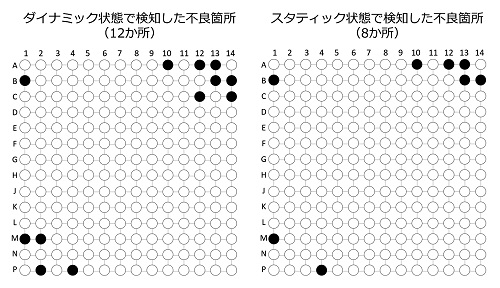

スタティック状態とダイナミック状態を比較すると、図13のようにHALT振動試験の結果に差異を確認した。

図13 ダイナミック状態とスタティック状態の不良検知箇所

図中の黒丸の箇所は、試験全体の中で各状態において、1回以上オープン不良を検知した箇所である。

ダイナミック状態で検出したオープン不良が12か所に対して、スタティック状態で検出したオープン不良は8か所となった。

この結果から、ダイナミック状態でテストを行うと、振動の影響で瞬間的にオープンした場合でも不良箇所として特定できるため、検出精度が高くなることがわかる。

ダイナミック状態とスタティック状態を含めたHALT振動試験全体での、時間経過に伴う不良検出数を図14に示す。

.jpg)

図14 試験時のJTAGテストによるオープン不良数の推移

HALT振動による影響で時間が経過するとBGAのボールが正常状態から半断線、断線と状態が変わっていく。

振動の影響によってサンプリングしたタイミングでBGAのボールと基板が接触しているか、接触していないかにより合否判定が変わるため、オープン不良箇所の検出数が上下に振れているが、時間が経過するにつれ、オープン不良が増えていることがわかる。

9. 断面観察の結果

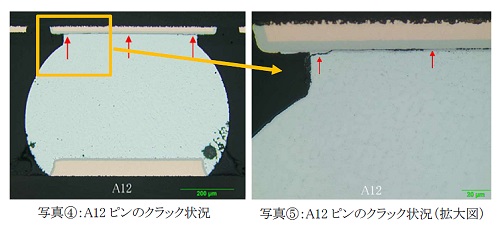

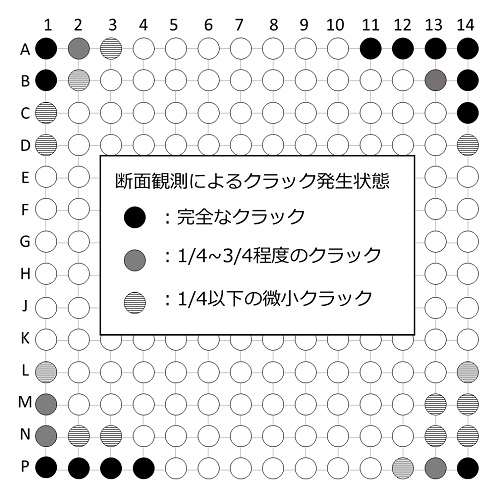

JTAGテストで特定したBGAのオープン不良箇所が、どのようなクラック状態であるか確認するため、図15の通り断面観察を行った。

図15 BGAの断面観察結果

A12ピンの断面観察結果より、JTAGテストで特定したボールの上面に、完全にクラックが発生していることが確認できた。

JTAGテストにより検知した不良箇所を検証するため、断面観察した結果を図16に示す。

図16 断面観察とJTAGテストの比較結果

断面観察で完全にクラックが発生している箇所に対して、30秒間隔でサンプリングしたJTAGテスト(図10)による検出率は88%であることが分かった。

この検出率は、サンプリング間隔を短くすることにより向上すると考えられる。

したがって、JTAGテストとHALT試験装置を組み合わせて使用することにより、製品基板に対してリアルタイムでBGAはんだの剥離状態をモニタリングできることが分かる。

10. まとめ

今回紹介したHALT試験装置とJTAGテストの組み合わせによる信頼性評価方法は、ダイナミック状態でJTAGテストを行うことにより、スタティック状態では検知できないオープン不良箇所を検知できることが分かった。

断面解析と比較しても30秒サンプリングで検出率は88%と高く、リアルタイムでBGAのオープン不良箇所をモニタリングすることができた。

HALT試験装置とJTAGテストを組み合わせた大きなメリットとしては、製品基板のBGAパッケージを試験対象にすることができること、また試験時間が2時間未満と非常に短時間で信頼性を評価できることである。

HALT試験が終わると、故障箇所を特定できているため、断面解析箇所を最小限に抑え、分析コストの削減と分析期間の短縮もメリットとなる。

分析結果は、プリント基板のレイアウト設計、はんだ材料、はんだの温度プロファイルなどにフィードバックすることにより、製品の信頼性向上と製品寿命を延ばすことができるようになる。

製品の信頼性向上に課題がある方は、お問い合わせいただきたい。

- 会社名

- アンドールシステムサポート(株)、エスペック(株)

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社

.gif)