1. はじめに

電子機器の小型化と高性能化が進んでいることは、多くの方が実感されているのではないだろうか。

実装技術が進化することにより、電子部品も小型のパッケージが増え、基板のサイズも年々小さくなっている。

電子部品では、FPGA、プロセッサ、メモリなどの基板を構成する主要部品の小型化でBGA部品が一般的に使われるようになった。

BGA部品のパッケージは、ボール間のピッチが1.27mmから1.0mm、0.8mm、0.5mmと年々狭くなり、さまざまな業界の製品で使われているFPGAの部品パッケージを調べたところ、図1のように小型製品向けの狭ピッチの部品パッケージが用意されていた。

図1 FPGA部品 パッケージの小型化

従来、BGAパッケージ部品の実装は、はんだ不良が少ないといわれていたが、これは過去の話だったようである。

実は、この数年間で不良基板が増え、お問い合わせいただく件数が増えている。

JTAGテストを活用して、お客様の故障解析をサポートする中で気付いたことは、0.5mmピッチの狭ピッチBGAを使い始めると、極端に実装不良が増えることである。

トラブルの症状はさまざまだが、試作基板だけではなく、量産基板でもBGAの実装トラブルが起こっており、深刻な状況になっている。

JTAGテストは、BGA実装基板のテストの課題を解決するため、多くの国内企業や海外企業が製造現場で活用している。

これまで当社では、10社を超えるお客様にご協力いただき、JTAGテスト導入事例を発表してきたが、製造検査、製品の保守、故障解析が中心であった。

今回は、品質保証と製品の信頼性向上に焦点を当てて、HALT試験装置とJTAGテストの概要、エスペック(株)の環境試験器とJTAGテストを複合した信頼性評価の事例を紹介する。

皆さまの製品に使われているBGAパッケージ部品の信性を向上するための新たな取り組みを紹介する。

2. エスペック(株)の紹介

エスペック(株)(図2)は、温度や湿度、圧力などさまざまな環境因子を人工的に再現する「環境試験器」を製造・販売しているメーカーであり、この分野における世界トップ企業である。

図2 エスペック(株) 本社(大阪市北区)

私たちの生活を支える電子機器や工業製品は、周囲の環境からさまざまな影響を受けている。

例えば、温度や湿度、圧力、光、振動、さらには電磁波など、周囲の環境を人工的に再現し、環境因子が製品に及ぼす影響を分析・評価することで、その耐久性や信頼性を確認する試験が「環境試験」であり、自動車やスマートフォンなどあらゆる工業製品の開発や品質評価において、環境試験器が用いられている。

今回の紹介する取り組みではQualmark社製(現・ESPEC NORTH AMERICA)のHALT試験装置を使用した。

Qualmark社は2015年にエスペックグループに加わり、2018年にESPEC NORTH AMERICAと合併した。

日本国内における製品に関するお問い合わせ、サポートはエスペック(株)が行っている。

3. HALTとは

HALT(Highly Accelerated Limit Test)は、製品化プロセスの初期段階である開発と設計において、短期間で製品の弱点を検出するための試験システムである。

1980年代に米国で発案され、欧米を中心に航空機、自動車、電気製品部品の信頼性評価に採用されている。

近年、HALTによる信頼性評価は欧米企業のみならずアジアにも拡大してきており、今後日本でも拡大していくことが予測されている。

HALT試験装置は、図3のように用途に合わせて、さまざまな製品が用意されている(https://www.espec.co.jp/products/qualmark/products.html)。

図3 HALT 試験装置(Qualmark社ホームページより。https://www.espec.co.jp/products/qualmark/products.html)

HALTは、製品の信頼性予測(寿命予測)を行うものではなく、製品仕様を超える「強いストレス」を製品に与え、製品の稼働限界と破壊限界を見つけるものである。

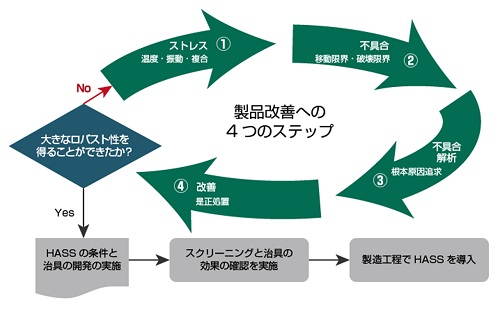

図4のように、製品の弱点を短期間で検出し、改善改良を繰り返すことで製品の信頼性を向上させることができる。

図4 製品改善への4つのステップ

「強いストレス」とは急速温度変化による温度ストレスと6自由度振動による振動ストレスであり、それらのストレス試験を組み合わせた5つのステップ(①低温ステップ試験、②高温ステップ試験、③温度急変サイクル試験、④振動ステップ試験、⑤温度急変と振動の複合試験)で構成されている。

4. BGAはんだ接合部の信頼性評価の課題

電子機器の小型化と高性能化に伴い、BGAパッケージ部品の小型化が進んでいる。

製品基板の検査は、不良品の市場流出を防ぐことと製品寿命を担保するための品質保証が重要となっている。

BGA部品において、はんだ接合部の信頼性評価試験が行われ、製品の品質保証が行われている。

従来はデイジーチェーン接続と呼ばれる配線設計された評価専用のBGA部品をメーカーから入手して、評価専用の基板を用意する必要があった。

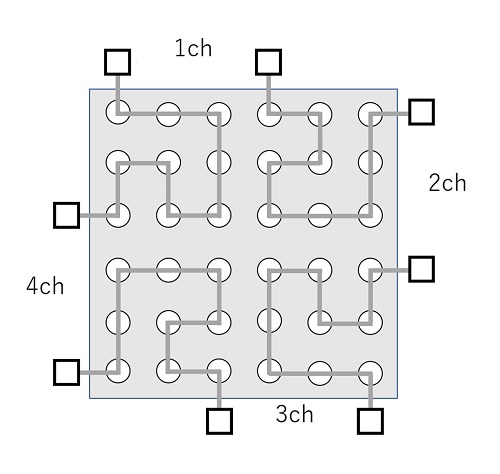

図5に示すデイジーチェーンの場合には、BGAのはんだ接合部を複数連続して繋ぎ、4チャンネルあるデイジーチェーンの抵抗値を測定することにより、抵抗値の変化でBGAのはんだ接合状態を確認することができる。

図5 BGA部品のデイジーチェーン

しかし、はんだ接合部をピンポイントで観察することができず、はんだ不良の箇所を特定するためには、断面観察等が必要となり時間を要すことが課題となっていた。

また、実際の製品基板は、製品用の配線になっているため、デイジーチェーン接続のBGA部品を実装して評価することができないため、BGAのはんだ接合部の信頼性評価を製品基板で実施する手法がなかった。

そこでJTAGテスト(バウンダリスキャン)を使い、製品基板を使って信頼性評価を行うことにした。改めて、JTAGテストの仕組みを紹介する。

5. JTAGテストとは

BGA実装基板に対して、テストのためにプローブピンではアクセスできない課題を解決するため、1980年代に次世代の検査方法を検討する団体「JTAG(Joint Test Action Group)」が発足した。

1990年に高密度実装基板のテスト手法として、バウンダリスキャンテスト(JTAGテスト)が「IEEE 1149.1」として規格化された。

現在ではIEEE1149.1 に準拠したCPUやFPGA、PLDが広く普及したため、JTAGテストは一般的なテスト方法の1つとなった。

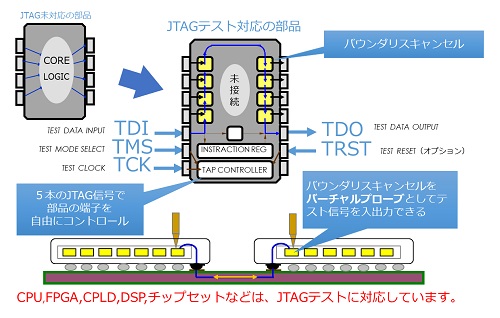

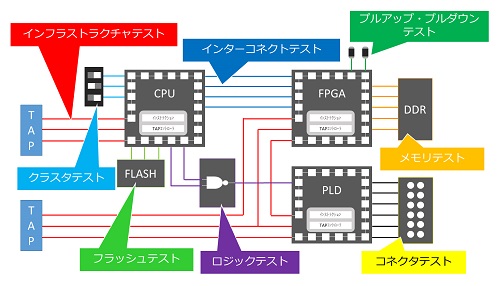

JTAGテストは図6に示すように、4本のJTAG信号(TDI(テスト・データ・インプット)、TDO(テスト・データ・アウトプット)、TCK(テスト・クロック)、TMS(テスト・モード・セレクト) から部品内部のバウンダリスキャン回路を制御する仕組みである。

図6 JTAGテストの仕組み

部品によっては、オプションでTRST(テスト・リセット)を含む5本の信号を使うこともある。

この4 本の信号から、JTAG対応のBGA部品の端子に内蔵されたバウンダリスキャンセルをバーチャルプローブとして利用して、JTAG対応部品間の配線テストとJTAGテストに非対応のDDRメモリに対してリード・ライトテストを行うことができる。

JTAGテストは通電試験によりBGA部品の型番、実装方向、ボンディングワイヤのテストと実装基板のオープン、ブリッジ不良、パターン不良を検出することができるため、近年の実装基板に対する有効なテスト手法の1 つとなっている。

JTAGテストを行うためには、JTAGテスト用のアプリケーションを作成する必要がある。

JTAG Technologies社の『JTAG ProVision』ではテストプログラムの作成が自動化されるようになり、誰でも簡単にJTAGテストアプリケーションを生成できるようになった。

JTAGテスト用のデータを生成するためには、基板を製造するために使用するネットリスト(回路CAD から生成される配線情報)、JTAG対応部品の内部のテスト回路情報が記載されているBSDL ファイル(部品メーカーより提供されるファイル)、JTAGテストに非対応の周辺部品ライブラリ(JTAGテストツールのライブラリ)を使用する。

自動生成したJTAGテストアプリケーションでは、図7のようにJTAGテスト対応部品間のテストであるインターコネクトテストの他に、28万種類を超えるJTAGテストに非対応部品のライブラリが用意されている。

図7 JTAGテストツールによる範囲の拡大

この部品ライブラリを利用して、DDRメモリ、ロジック回路、フラッシュメモリ用のテストアプリケーションが自動生成される。

そのため、飛躍的にテストカバレッジは拡大し、ファンクションテスト開発と比較するとテストデータ作成にかかる工数を大幅に削減できるようになった。

当社が公開しているJTAGテストのユーザー事例では、画像処理用の実装基板に適用した結果、JTAGテストのみで約85%のテストカバレッジが得られた例もある。

今回、HALT試験装置とJTAGテストを結合して評価するために、ザイリンクス社のFPGA(BGA 196ピン)を実装した基板をターゲットとした。

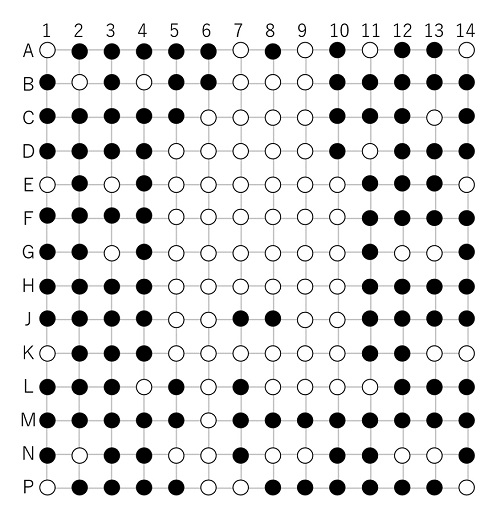

FPGAのピン配置とバウンダリスキャンセル(バーチャルプローブ)が内蔵されているピンを図8に示した。

図8 FPGA内のバウンダリスキャンセル

(●:バウンダリスキャンセル内蔵のIOピン ◯:非内蔵の電源、GNDピン)

FPGAの場合には、黒丸のIOピンはすべてバウンダリスキャンセルが内蔵されているため、製品の周辺回路を制御してテストすることができる。

白丸のピンは、電源、GNDであるが、バウンダリスキャンセルは内蔵されていないが、JTAGテストは、ファンクションテストと同様に、電源が正しく投入されていないと機能しないため、JTAGテストが実行できれば電源とGNDが正しく投入されていることが分かる。

- 会社名

- アンドールシステムサポート(株)、エスペック(株)

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社

.gif)