⑤JTAGポートを閉じることはCRAの理念に合わない

JTAGポートは、実装基板の検査・デバッグに広く使われている標準インタフェースである。このJTAGポートを利用して、実装基板上のJTAGテスト(以下、バウンダリスキャン(IEEE 1149.1標準規格)を操作して、IC間の接続状態を論理的に検査できるため、多層基板や高密度実装でプローブが困難な場合でも有効である。量産工程では断線・ブリッジの検出、部品実装の確認、簡易I/O検査などに活用される。

一方で、JTAGポートは、内部に入るための入口でもある。マイコン、SoCによっては、レジスタアクセス、メモリアクセス、フラッシュの読み出し/書き換え、CPU停止など、ソフトウエア開発時のデバッグに必要となる強力な機能を提供する。これが出荷後も無制限に使える状態で残ると、プログラムや秘密情報(暗号鍵・証明書・設定)の漏えい、改造、クローン作成などのリスクが高まる。

重要なのは、JTAGポートが危険なのではなく「制御されていないJTAGポート」が危険だという点である。CRA対応では、JTAGポートを含むインタフェースを「どの段階で、どの権限で、何に使うか」を定義し、その通りに設定されていることを検査で示すことが重要になる。

CRA対応の議論で注意するべきことは「危険ならJTAGポートをすべて無効化すべき」という結論である。もし、JTAGを完全に無効化すると、バウンダリスキャンが使えなくなってしまうため、出荷後の故障解析や不具合調査が著しく困難になる。実装基板の不具合は、はんだクラック、部品劣化、ESDダメージ、コネクタ接触不良など、時間経過や使用環境で顕在化する。

これらを解析する際、バウンダリスキャンテストが使えるかどうかで、原因切り分けの速度と精度が大きく変わってくる。解析手段を失うと、原因不明のまま基板交換や製品回収が増え、コスト・納期・環境負荷(廃棄増)に直結する。さらに、CRAが掲げる「レジリエンス」とは、単にセキュリティ保護だけではなく、「問題発生時に回復できる能力」を含んでいる。したがって、解析性を完全に放棄する設計は、CRAの理念とも整合できなくなってしまう。

図4に一般的なJTAGポートのセキュリティレベルを示した。セキュリティレベルを高めつつ、検査、故障解析による機器の回復能力を維持するためには、バウンダリスキャンのみ有効にすることを推奨する。ただし、求められるセキュリティレベルは、取り扱う情報と機器の用途により、どのレベルにすべきか検討する必要がある。

図4 JTAGポートのセキュリティレベルの設定例

⑥ファンクションテストで使うLAN・UARTの危険性

ファンクションテストでは、LANやUART(シリアル)が多用される。これらは初期設定、ログ確認、通信試験、製造設定の投入などに便利である一方、出荷後に残存すると侵入口になりやすい。UARTは特に注意が必要で、ブートローダ操作やOSシェルへのアクセス、診断コマンドの実行を許す構成が現場では珍しくない。LANについても、テスト用サービスやデバッグポート、初期パスワード、テスト用証明書などが残れば、ネットワーク越しに攻撃される可能性がある。

ここで重要な考え方は「性質の違い」である。UARTやLANはOS・ネットワークスタックと直結し、攻撃がソフトウエア層まで一気に到達しやすい。ソフトウエア層には、守るべき情報資産へのアクセスができてしまう可能性が高い。一方、バウンダリスキャンに限定されたJTAGポートは物理層に近く、ネットワーク経由では侵入できない。また、情報資産へのアクセスは困難である。したがって、LAN/UARTは原則として出荷時に閉じるべきであり、「JTAGポートは制限して管理する」という方針が合理的と考えられる(図5)。

図5 CRA観点で見るUARTとLANの危険性

⑦検査ファーストを設計段階で検討する

「検査ファースト」とは、製品の性能とコストだけに目を向けるのではなく、「検査を重視する」考えである。設計、デバッグ、試作検査、品質保証、量産検査、保守のすべての製品ライフサイクルで、テストを容易に実現するためには、設計段階からテスト容易化設計により、バウンダリスキャンを活用できる工夫が重要となる。

CRAに対応した「制限付きのJTAGポート」を実現するためには、検査でJTAGポートが機能制限されていることを証明する必要となる。設計書に「制限する」と書いても、製造手順、治具の設定、書き込み手順の差で、量産品の状態が設計意図から外れることが起こり得る。CRAの観点では、設計意図だけでなく、出荷個体が安全であることを証明する必要がある。

出荷前検査では、JTAGや各種インタフェースの状態を必ず確認し、結果をログとして残すことが求められる。例えば、「JTAGが制限モードであること」、「フルアクセスが無効化されていること」、「UARTのテスト機能が閉じられていること」、「LANのデバッグ機能が閉じられていること」などを定量的に確認し、ロット・シリアル単位で追跡できるようにする。これにより、CRAが求める説明責任に耐え得る工程となる。

さらに検査ファーストでは、「出荷後にJTAGポートからバウンダリスキャンテスト機能を残すべき理由」を、設計思想ではなく検査工程の延長として整理しておくことが重要である。JTAGポートを出荷時に完全無効化すると、セキュリティ上の安心感は得られる一方で、フィールドで発生する物理故障や品質劣化に対する故障診断手段を失う。

出荷後にバウンダリスキャンを残す主な理由とメリットは次のとおりである。

1. 故障解析の再現性と切り分け速度が向上する

フィールド不具合は「再現しない」「症状が揺れる」ケースが多い。バウンダリスキャンはOSやファームウエアに依存せず、IC間接続の電気的健全性を論理的に検査できるため、断線・接触不良・ブリッジなどの物理要因を短時間で切り分けられる。結果として、原因不明のままの基板交換や過剰なソフトウエアの疑いを減らせる。

2. 高密度実装における「見えない不良」箇所を特定できる

BGAや微細ピッチ部品では、外観検査やプローブアクセスだけでは検査が困難である。バウンダリスキャンを残しておけば、非破壊で信号線の導通確認やピン状態確認を実施できる。特に長期使用後のはんだクラックやコネクタ劣化に対して有効である。環境試験装置と組み合わせて、温度サイクル、振動試験と組み合わせてバウンダリスキャンを実行して、市場不具合の再現性を向上できる。

3. リコール・サービスコストの低減につながる

解析手段が乏しいと、現場では「安全側」として基板総交換になりがちである。バウンダリスキャンによる切り分けが可能であれば、故障箇所の特定と修理判断が迅速になり、在庫・物流・廃棄を含むトータルコストを下げられる。これは環境負荷(廃棄物削減)の観点でもメリットがある。

4. レジリエンス(回復力)を支える「正規の診断口」になる

CRAが求めるレジリエンスは、攻撃を防ぐだけでなく、問題が起きた際に回復できる能力も含む。制限付きバウンダリスキャンは、情報漏えいや改造につながる機能を閉じたまま、正規の診断・品質解析のための手段として機能する。

5. 「残してよい理由」を説明しやすい(監査適合性)

JTAGポートを残すこと自体が問題ではなく、残し方が問題である。検査ファーストの枠組みで、「許可機能はバウンダリスキャンのみ」、「デバッグ機能による書き換えやメモリアクセスは禁止」という設定を行えば、「攻撃されるリスクを削減しながら検査性を維持する」という説明ができる。

以上のように、検査ファーストは「出荷前の確認」で終わるのではなく、「出荷後の品質・保守まで見据えた設計と検査の整合」を作る考え方である。バウンダリスキャンを制限付きで残すことは、CRA対応と実装現場の合理性を両立させる具体策の一つとなる。

- 会社名

- アンドールシステムサポート(株)

- 所在地

-

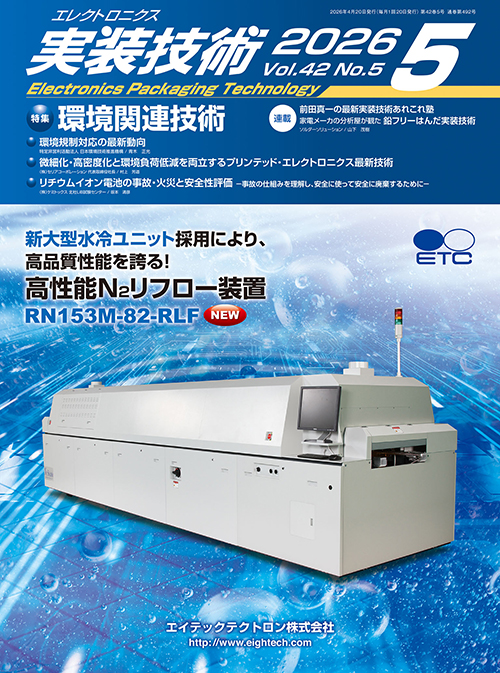

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社

.gif)