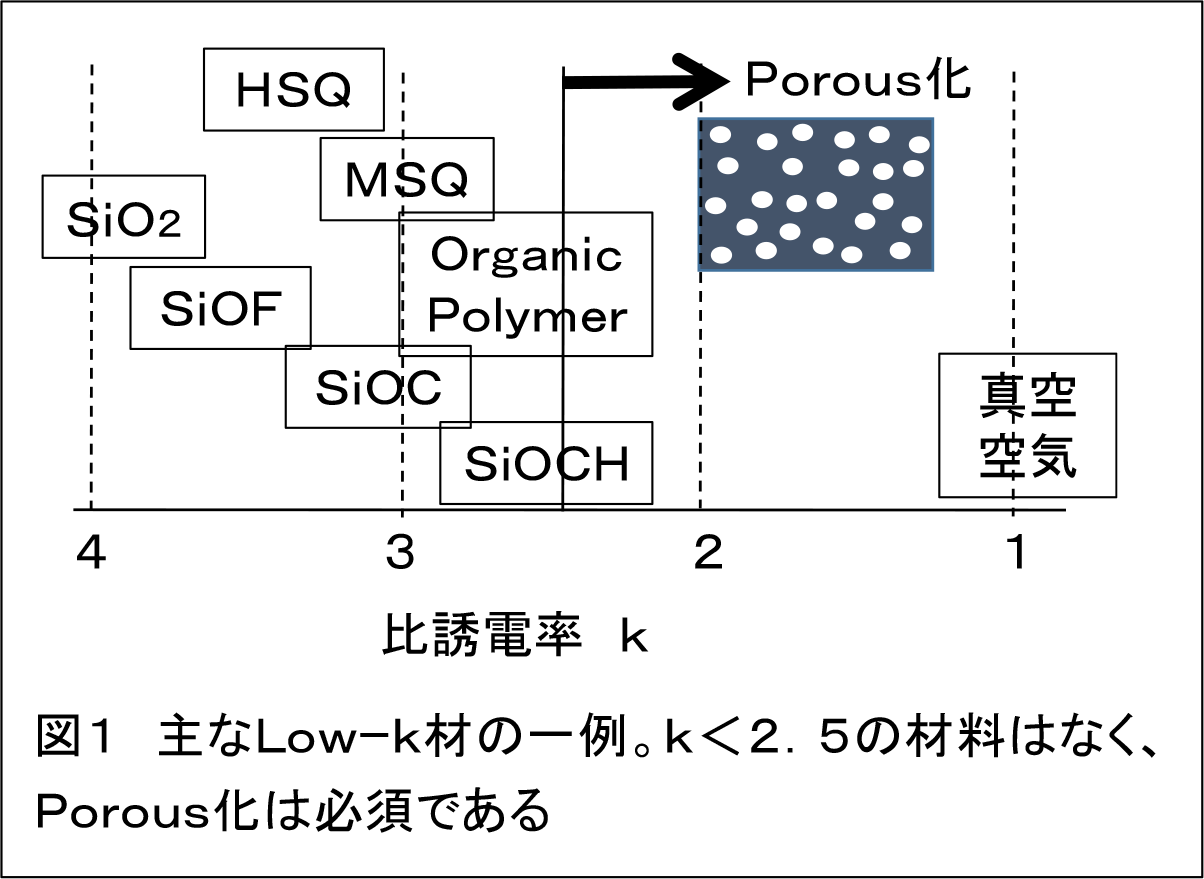

3. ポーラス膜の製法と問題点

ポーラス膜の製法は、溶液による塗布方法とCVD(Chemical Vapor Deposition)の2種類がある。

各社ごとに使用する材料やプロセスのノウハウがあって標準的な製法はないと思われるので、以下は一例である。

塗布する材料として、シリカ前躯体と界面活性剤を混合した液をウエハ上に塗布し、数百℃の温度で加熱すると、シリカの薄膜が生成しその中に界面活性剤による空孔ができる。

成膜条件にもよるが、数nm程度の径の空孔ができ、界面活性剤の量を変えるとkの値を変えることができる。

空孔の数が多くしても機械的強度が弱くならないように、対策として有機ケイ素化合物でシリカ骨格を補強したり、焼成温度を上げるなどが行われている。

ポーラス膜の問題点の一部を図4に示す。図4の①Aは、空孔がエッチングした溝の表面に顔を出している場合で、その後、溝の中に銅配線する場合の薄いバリア金属の均一性がなくなる。Bのように空孔が連続していると、ここを水分が侵入してk値を上げてしまって空孔の効果がなくなってしまう。

図4の②は溝の表面から水分やガスが侵入しないようにバリア層を設けた例で、図4の③は空孔の径を小さくして空孔が連続しても影響がないようにした例である。

.png)

4. エアギャップの製法

配線の間隔が狭いとその部分にCVDで膜を入れるのが難しく、空洞ができてしまう。

以前は空洞ができないように努力していたが、逆にLow-k化には空洞ができるのがメリットになった。

配線間の狭い部分のk値を下げることができるので、空洞の効果は大きい。 図5は、CVDで空洞ができる様子を表している。すなわち、CVDのガス流がトレンチの底まで垂直に流れていると、図5の①のようにトレンチ底から順に膜が成長する。

いっぽう、図5の②のようにひさしのあるようなトレンチの場合はガス流が

平行でなくなり、トレンチの底だけでなく側壁からも成長して、図に示したように大きな空洞ができる。

完全なエアギャップではないのでk=1ではないが、側壁の膜で強度が少しは補強されている。

.png)

図6は、LSIの配線の様子を表したもので、一般に下層の配線は微細であり、層間膜としてLow-kが要求される。

いっぽう、上層が太い配線なのでLow-kの必要がない。機械的強度は下層が軟弱であるが、上層が硬くてしっかり押さえているので、後工程でのCMP研磨やワイヤボンドの機械的応力にある程度は対処できる。

.png)

2. SOIによる低容量化

SOI(Silicon on Insulator)は、古くからあるデバイス構造で多くのICが生産されてきたが、微細化が進むと図7右のようにSiのチャンネル層の厚さが10nm以下に薄くなってきた。

従来のMOS構造では、図7左のように接合の空乏層容量が大きいが、SOI構造だと容量が極めて小さく動作速度が向上する。

.png)

現在、10nmノードのLSIが生産になっているが、SOI構造の場合は15nm程度でもほぼ同等の特性が得られている。 SOIはウエハの製造には凝った方法が必要で、フランスのSOITEC社が開発した図8の方法が用いられている。

.png)

ウエハは高コストだが、製造プロセスコストがそれ以上に高コストになったため、性能を重視するLSIではSOIが用いられている。

以上、今月は配線の層間膜を中心に見てきた。来月は、微細化に伴って縦方向も微細化が必要になり、ゲート酸化膜が1nm程度になって大問題が発生した話を取り上げたい。

- 会社名

- 厚木エレクトロニクス

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社

.gif)