開発の背景

近年、車載電子機器は大きな3つの流れがある。

まず、新興国市場の台頭により低価格化が進んでいる。

ここでの具体的な半導体デバイスに対する要求としては、低価格車中心の市場であるため機能が絞り込まれ簡素な車両構造のため、①電源環境の悪化への対応、②不要輻射の部品レベルでの低減、がある。また、この新興市場の多くは熱帯/亜熱帯/多雨地域にあるため、③耐高温多湿環境の向上、④消費電力の低減(動作温度の上昇の抑制)が望まれる。

次に、環境問題や資源問題からくる動力の多様化がある。電気自動車が台頭しているが、その課題は実用的な走行距離の確保であり、極限の軽量化・低電力化が要求されている。軽量化においては、デバイス自身の小型のみならず、重量部品の削減、具体的には放熱やノイズ対策部品の削減が重要である。低電力化においては、①低電圧化、②動作電圧制御、③パワー素子の高効率化、④レジュム機能からの高速復帰、などの要求がある。

3つ目は機能安全への対応である。カメラやレーダ、ソナーを使った運転支援装置が多く実用化しているが、最近では操舵系を制御する製品も見られ、最終的には自動運転への挑戦が行われている。このような機器ではとりわけ致命的故障は回避されなければならず、半導体デバイスに対しても、①電源系の高信頼性化(電源回路の低インピーダンス化)、②接続信頼性の向上(ソリッドステートでの一体化)、③部品点数の削減、④処理の多重化・多様化(高速不揮発性メモリや異なる回路形式/部品/材料の併用)、などの要求がある。

これらの要求に対し半導体の3次元集積化は一定の解決方法を与える。

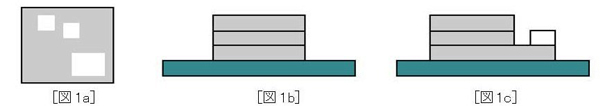

図1aは、不要機能(白色部分)を削減し、電源安定化のためのキャパシタにすることで、電源安定⇒低電力化⇒低発熱⇒高温対応するアイデアを示したものである。キャパシタ加工のチップコスト上昇は周辺部品の削減で吸収できる可能性がある。

図1bは、パスコン層・マイコン層・高速不揮発性メモリ層と3層に積んだマイコンの例である。メモリ層を分離することで、高速不揮発性メモリの集積を容易に実現できるため、①暗電流ゼロ、②高速復帰、が実現される。マイコン層も大容量メモリが分離されることで工程の最適化を行うことができ、コストや電力の低減が期待できる。また、パスコン層を直下に内蔵することにより電源の低インピーダンス化が実現され、①低電力化、②低EMC化、が実現される。パワーTrに関しても、高速不揮発性メモリ層と同様な考えを取ることが可能である。

図1cは、運転支援装置のために高信頼性化されたマイコンの構成例を示す。メモリ層やマイコン層は図1bと同様だが、パスコン層に多重化の制御を行わすこと、たとえば高温まで動作する異種半導体によるバックアップ回路(白色部分)を集積することなどによって、機能安全性を高めることができる。ソリッドステート集積による部品間接続や、ヘテロ積層による処理多重化/多様化などは、3次元LSI特有の利点として、機能安全のみならず新機能の実現に寄与すると思われる。[複合センサ+アンプ+通信回路] などの集積もその例である。

図1 半導体の3次元集積化の形

これらのアイデアはいずれも前述の市場要求に合致しているため、近年、車載電子機器のおいても3次元集積化への要求が高まってきている。

特徴とその優位性

今回開発したTSV(シリコン貫通ビア)を利用したデカップリングキャパシタは、特に車載環境など電源が不安定な環境で低電力設計されたLSIを安定して動作させるためのアイデアで、デカップリングキャパシタを含む低インピーダンスのSiインターポーザを狙ったものである(今回は試作の都合で、デカップリングキャパシタのウエハとSiインターポーザのウエハを別々に試作し積層したが、本来は1枚のウエハにインタポーザとデカップリングキャパシタの機能をもたせるのが合理的であり、今回の試作においても同一プロセスで試作できることを意識した)。

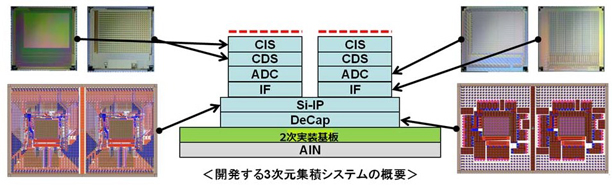

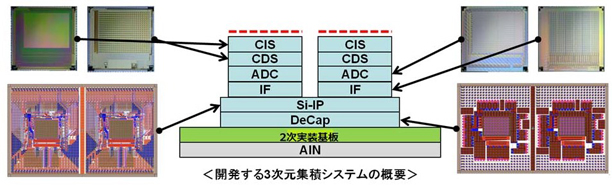

その具体的なデバイス例として、図2に示すようなデジアナ混載3次元画像センサモジュールを開発している。イメージセンサは、相互干渉のない安定した多電源の供給ができて初めて所定の性能が発揮されるデバイスであるため、リーディングデバイスとしては最適であると考えた。

図2 デジアナ混載3次元画像センサモジュール概要

また3次元デバイスは、3次元化された後での動作不安定はその解析性の悪さから致命的であるので、設計時に十分マージンをもって安定動作をさせる考慮できるか課題になる。

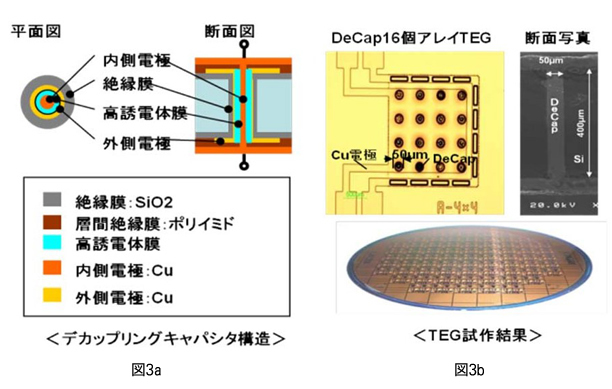

図3aに、今回試作したTSV型デカップリングキャパシタの構造を示す。通常のTSVに高誘電体膜を挟み込んだ同軸構造をもち、パスコンを形成する。

図3bはそのレイアウト(16セルが並列な構造である)、試作の断面写真、試作ウエハの全景写真である。

図3 TSV型デカップリングキャパシタの構造とTEG試作

- 会社名

- 技術研究組合 超先端電子技術開発機構(ASET)

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社