システムレベルでの検討や設計レビューの必要性

スマートフォンやタブレット端末などデジタル情報家電では小型高密度化が進行しており、詳細設計や試作まで進んだ後に問題が発覚すると、そこからの設計変更は大きな手戻りを招く。

たとえば、ノイズ要因を調査してLSIと周辺配線がノイズ源だと判明すると、大規模な配線変更や、部品の追加変更を行わなければならない。こういう手戻りを排除するためには、設計段階で半導体/パッケージ/プリント基板をシステム全体視点でとらえて、配線や電源の配分を最適化しておく必要性がある。

しかし半導体やパッケージ、プリント基板は、別部門や異企業の担当者によって設計されるため、設計検証は、設計が完了する直前に、電話やメール、エクセルシートなどを介して人間力に頼った『すり合わせ』で行われている。

CR-8000の新たな協調設計ソリューション

CR-8000 Design Forceでは、複数のプリント基板をCADに読み込んで基板間接続部も含めてシステムとして設計や検証を行うマルチボード設計環境を提供する。設計対象物は、プリント基板に限らずパッケージや半導体など異なった構造物でも、同じデータ上で扱えるようにしている。

従来は設計対象物によって別なCADを使う必要があったが、Design Forceでは半導体/パッケージ/プリント基板を接続した状態のまま、設計検証することが可能になった。また、複数設計者が異なったオフィスや場所から、ネットワークを介して設計データを共有し、システム全体を見ながら配線の引き回しやピン配置を協議/検討することもできる。

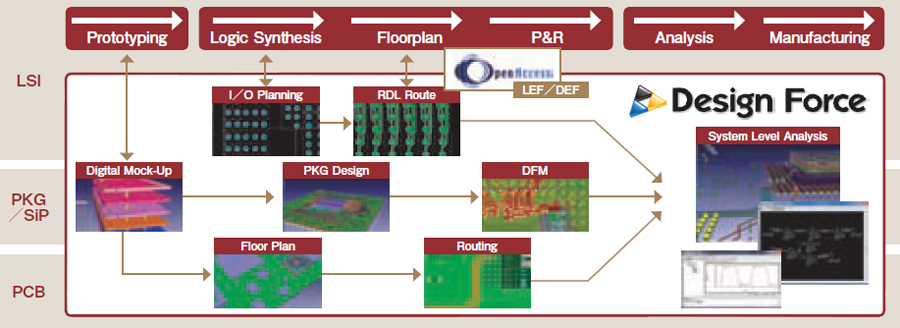

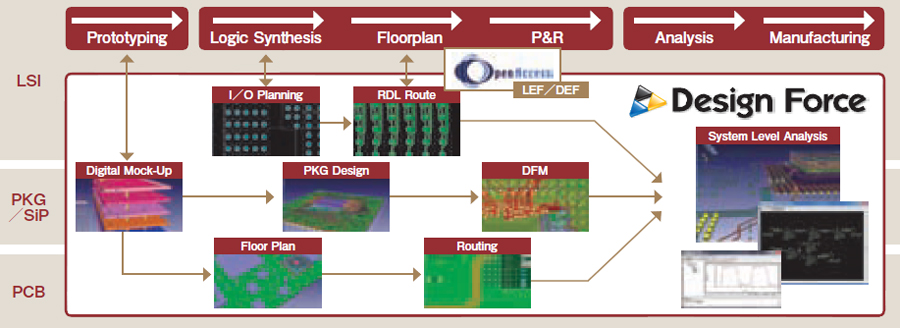

このマルチボード設計や半導体/パッケージ/プリント基板協調設計の仕組みは、次のようなDesign Forceの豊富な設計検証機能と組み合わせて使うことができる(図1)。

図1 協調設計のフロー

●パッケージやPCBの制約を考慮したチップ側のI/O決定

●チップ側の制約を考慮したパッケージやPCB側のI/O決定、電源配分

●マルチエリアならびにマルチボードでの同時並行設計、協調設計

●マルチボードでのコンストレインツドリブン設計

●半導体のスタックや並列配置に対応した3次元実装機能

●配線、面、ビアの構成の3次元表示編集、ダイナミックな層構成やテクノロジの編集

●異なる基板や構造物をまたぐシステムレベル信号のSI解析や検証

●FPGAベンダーが提供するデザインキットやツールとの連携

●エリアや層ごとの自動配線指定、複数領域での同時自動配線実行

●アクティブ素子の内層実装を支援する内蔵部品設計支援機能

Synopsys社とのアライアンス

半導体との協調設計を行うには、半導体やパッケージ業界で流通する設計データを取り込む必要がある。

当社は、半導体EDA分野をリードするSynopsys社とアライアンスを結び、設計構造物の垣根をこえたシステム全体の設計検証実現を目指している。また、LEF/DEF※1やOpenAccess※2、LPB※3など様々なデータフォーマットによる半導体設計環境との連携に取り組んでいる。

今後Design Forceは、プリント基板も含めた3D-ICの設計環境構築と構造物の壁をまたぐコンストレイント情報流通の拡張を進め、半導体、パッケージとプリント基板の設計技術やプロセスの壁を取り払っていく。

※1 LEF/DEF

レイアウト設計用EDAのデータ標準形式

※2 OpenAccess

半導体の設計を行うための標準データベース

※3 LPB

JEITA LPB-WGによる半導体、パッケージ、プリント基板の相互設計支援フォーマット

- 会社名

- (株)図研

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社