1. 配線のCR値を下げる工夫

先月号では、回路の抵抗Rとコンデンサ容量Cの積であるCR時定数が大きくなると回路の周波数特性が悪化することを説明し、CRの内、抵抗Rを下げるための対策について議論した。今月は容量Cを下げる工夫を取り上げる。

1. 配線の層間絶縁層はLow-kに

配線の層間絶縁膜は、古くからSiO2またはBPSG膜(Boro-Phospho Silicate Glass:ホウ素リンガラス)が用いられ、比誘電率k≒4.0である。

誘電率の表記は、物理関係ではεであるが、回路関係ではkが用いられ、低誘電率をLow-kと呼んでいる。コンデンサの容量値は、電極版の面積をA、電極版の間隔をdとすれば、容量Cは次式で表される。

LSIの微細化が進むと、配線の断面積に相当する上式のAもある程度小さくなるが、dはますます小さくなって、容量Cは大きな値となってしまう。

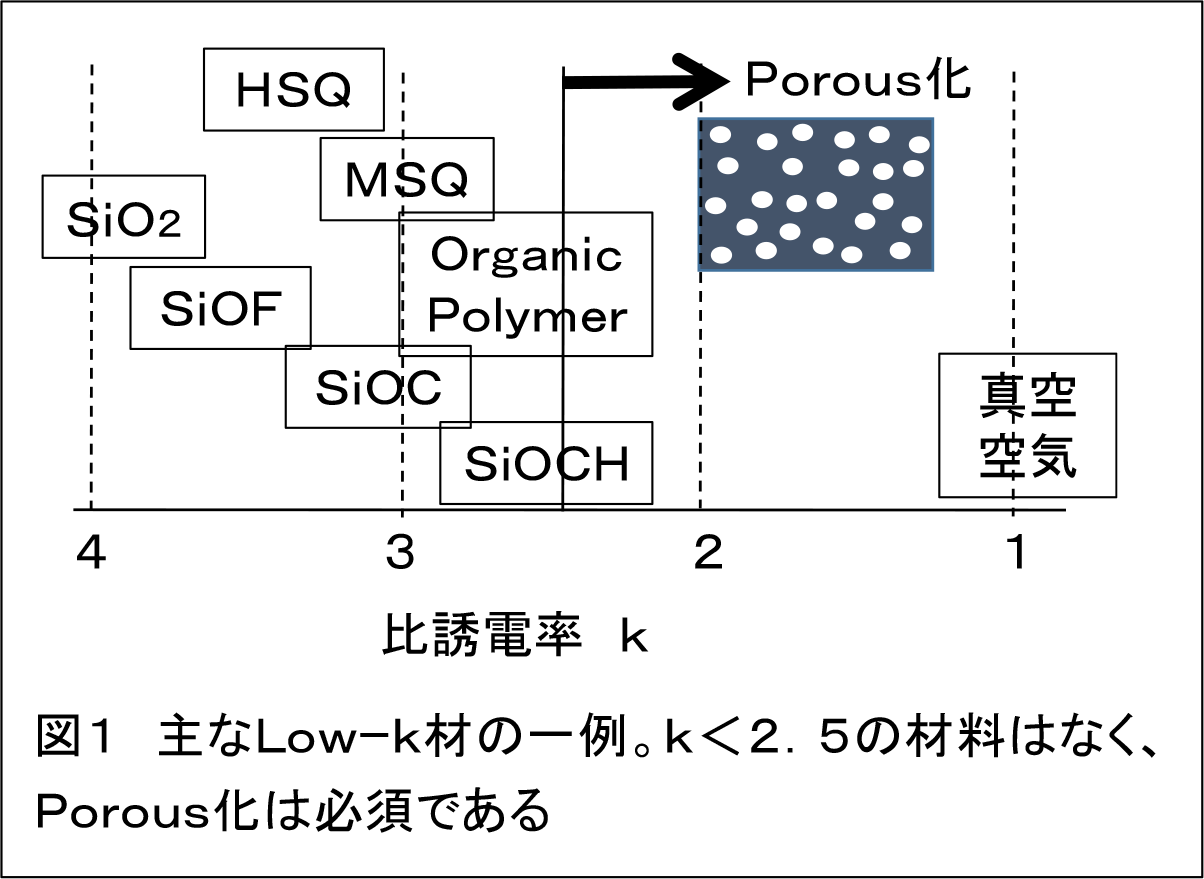

そこでCを小さくするにはkを下げることが重要となる。Low-k膜としてCVD材料なら、SiOF(k=3.4?3.8)、SiOC(k=2.5?3.0)などが用いられ、有機物系のスピンコートできる材料も使われている。

図1は主なLow-k材料である。

.png)

2. ポーラス膜でLow-k化

真空ならk=1でそれ以上に低いk値はないが、現実のLSIの配線層間を真空や空気(真空とほとんど同じk=1)にすると、配線を支えるものがないぶらぶら構造ではとても製品にはならない。

そこで、通常の膜と真空の中間的なポーラス(Porous:多孔質)膜が用いられている(図2上)。

.png)

ポーラス膜の空孔率(Polosity)を高くすると誘電率は真空に近くなり下げられるが、スポンジのような柔らかい膜になってしまい、後のプロセス中に機械的応力が掛かった場合に変形し破壊されるような問題が発生する。

また、空孔の中に水分などが入ると、誘電率が大きくなってしまう。

図2下は、配線間に大きな空洞を作ってk値を2.5以下に下げた例である。

空孔率を大きくすると誘電率は下げられるが、図3に示すように機械的強度が弱くなり、トレードオフの関係である。

.png)

- 会社名

- 厚木エレクトロニクス

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社

.gif)