1. はじめに

CMOSが微細化されると、大きな電流が取れなくなり、移動度を向上する必要が出てきた。今月は移動度向上のため、結晶に歪みを与える話題を取り上げる。

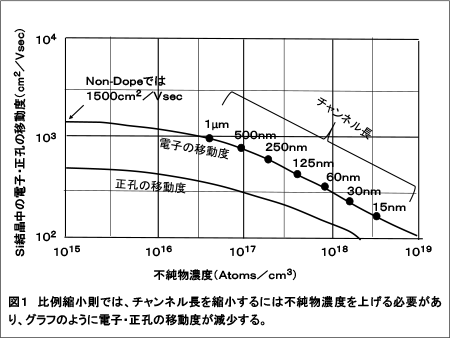

比例縮小則によると、微細化が進むほどチャンネル部の不純物濃度を上げる必要があり、不純物濃度が上がると電子や正孔の走行が邪魔されて、図1のように移動度が下がる。また、微細になるほど表面の影響が大きくなり、表面の再結合中心に電子や正孔がトラップされて移動度が下がる原因となる。

.png)

MOSの駆動電流は図2で表され、移動度に比例するので、微細になって移動度が下がるほど駆動電流が減少し、CMOSLSIの設計が困難になってきた。

.png)

移動度を高くするため、IBMは図3のような結晶に歪を与える方法を発表した。Siに比べてGeは原子半径が大きいので、Si結晶中にGeを入れると結晶が膨張する。

.png)

エピタキシャルにSi/SiGe/Siと結晶成長させると、大きなGe電子が入っているのに格子間隔は下地と同じであり膨張できないので、圧縮応力が発生する。ちょうど満員電車に太った人が乗ってくると圧縮歪が発生するようなものである。

圧縮応力が発生すると、一般に正孔の移動度が向上し、逆に引っ張り応力の場合は、電子の移動度が向上する(結晶軸の方向によっては、必ずしもこの通りではないが)。

IBMの発表をきっかけに、いろいろな歪の与え方が研究され、現在は図4のような方法が実用化されている。

.png)

すなわち、ソースとドレインにGeをドーピングして膨張させると、チャンネル部が押されて圧縮され、正孔の移動度が上がる。

Geではなく原子半径の小さいC(Carbon)をドープすると引っ張り応力が発生し、電子の移動度が上がる。GeやCをSi中に入れるプロセスは、図5のようにソースとドレインのSiをエッチングして除去し、その跡にGeやCをドーピングしたSiをエピタキシャルに成長させる。

.png)

GeやCの濃度は20%程度で、あまり大きな割合でドーピングすると、エピタキシャルでなく結晶が乱れて欠陥が多くなって歪がなくなりストレスがかからなくなってしまう。

さらに簡便な方法としてSMT(Stress Memorization Technology)がある。

ゲート電極の上にSiN膜をCVDでカバーすると、図6のようにポリシリコンを介してチャンネル部にストレスがかかる。この状態で熱処理すると、熱をとった後でもストレスがそのまま残る。そこで、Stress Memorize(歪を記憶)と呼ばれている。

.png)

SiNの生成方法によって、圧縮や引っ張り応力が発生し、チャンネル部に影響する。SiN膜はSiO2などの膜に比べてかなり硬いので、このような効果が起る。プロセス上は簡単に実現できるので多用されている。

以上のように、Siに歪を与えることにより電子や正孔の移動度を向上させ、LSI微細化に伴う駆動電流の減少を防ぎ、動作速度の向上を得ている。

次月は、LSI微細化プロセスの中心話題であるフォトプロセスによるパター二ング技術について取り上げたい。

- 会社名

- 厚木エレクトロニクス

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

話題のGlass PKG実装技術の動向 〜先端電子部品への応用と 最新のCuダイレクトめっきGWCについて〜 Grand Joint Technology Ltd 大西 哲也(T. Onishi)Gichoビジネスコミュニケーションズ株式会社

.gif)