1. はじめに

先月号では、LSIの集積度が年々増加するというムーアの法則を示し、その主な技術としてパターンの微細化が重要であることを述べ、CMOSの簡単な説明を行った。比例縮小則の示すところでは、微細化により集積度が上がるだけでなく、LSIの性能も向上することを述べたが、いっぽう、表1のような多くの弊害があらわれるようになり、その解決のためLSIの構造が複雑になってきた。今月はその解説を行う。

.jpg)

表1 CMOSLSIの微細化に伴い発生した諸問題(先月号の再掲)

2. 短チャンネル効果の抑制

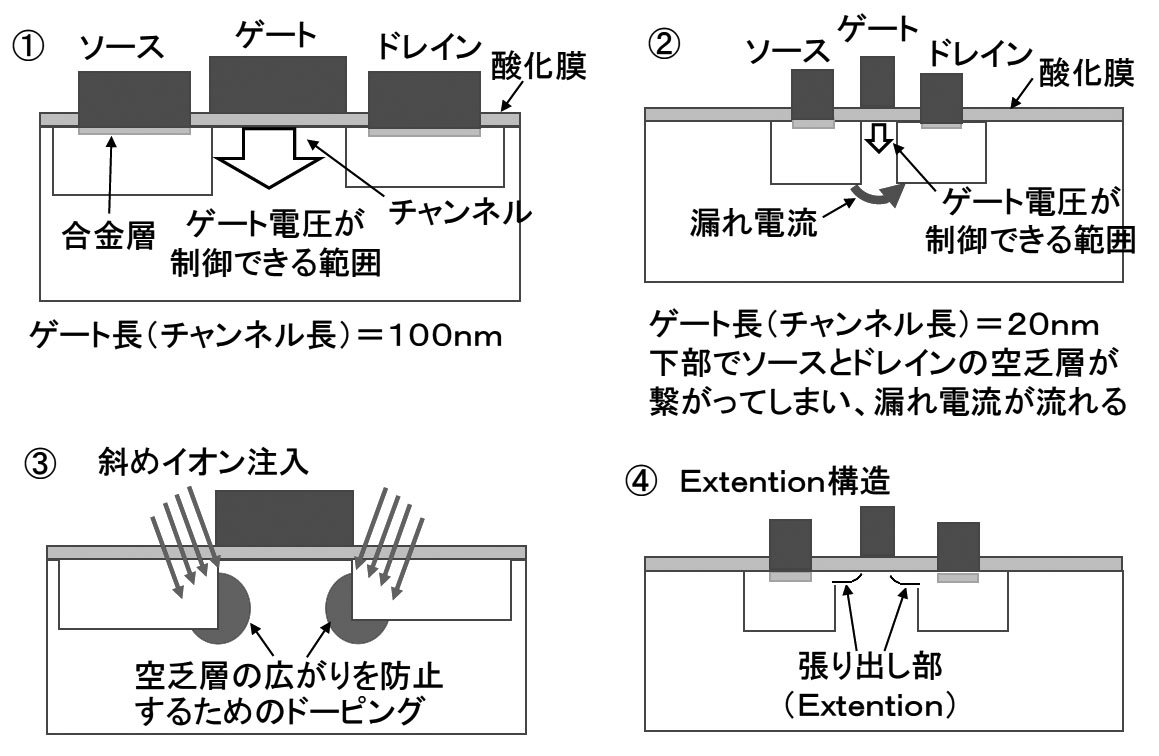

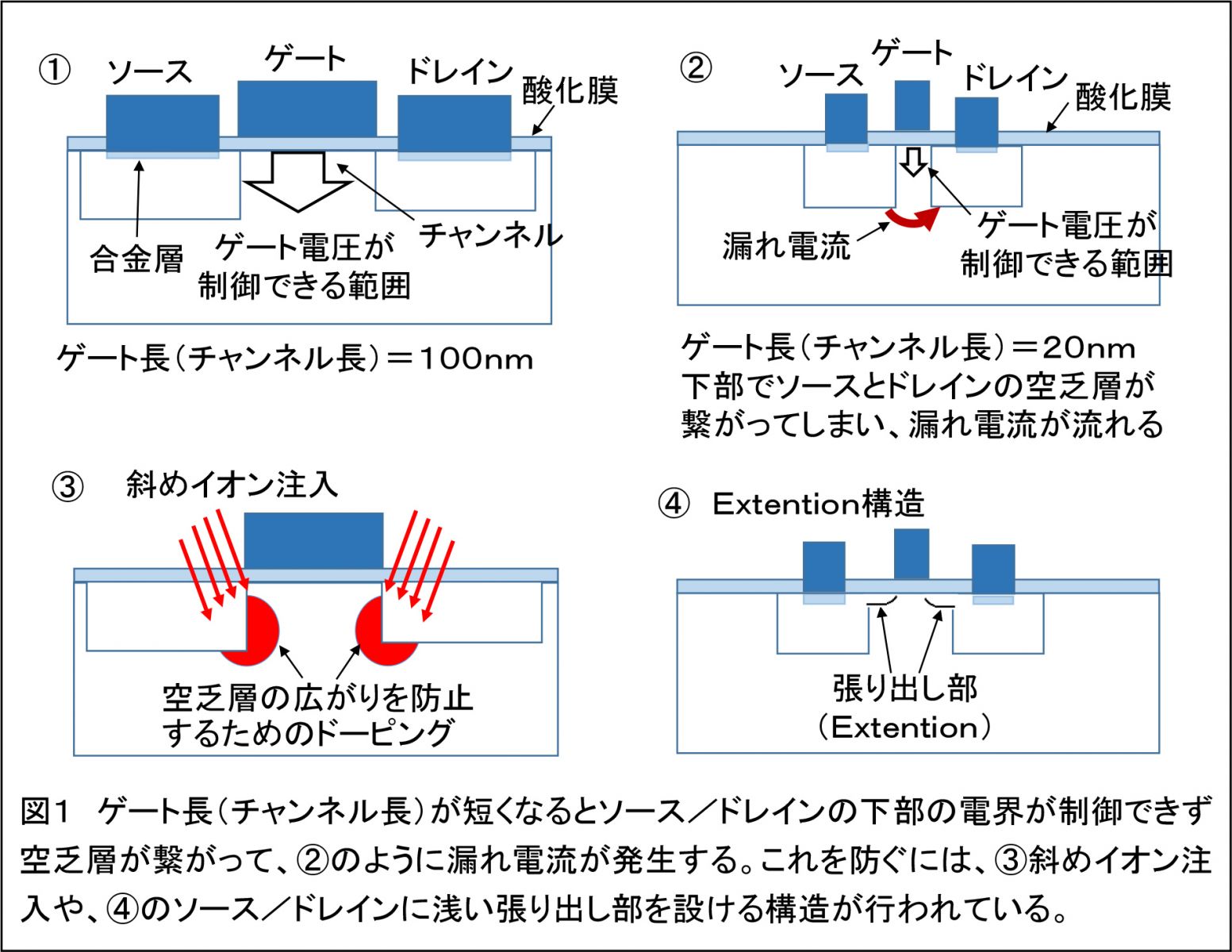

MOSトランジスタのゲートの寸法がソース/ドレインの深さ方向の寸法と同程度の場合は、図1の①のようにゲート電極からの電界でトランジスタ動作が正常に行われる。ところが、平面上のパターンをどんどん微細化し、結晶内部への寸法をそのままにすると、図1の②のようにゲート電極からの制御が困難となり、ドレインからの空乏層が伸びてソースとドレイン間に漏れ電流が発生する。これを防ぐには、図1③のように斜めのイオン注入によりチャンネルの深い部分の濃度を高くして空乏層の広がりを防ぐ方法や、④ソースとドレインから浅い張り出し部(Extentionと呼ばれる)を設けるのが良く、現在の2次元MOSでは全てこの張り出し構造になっている。

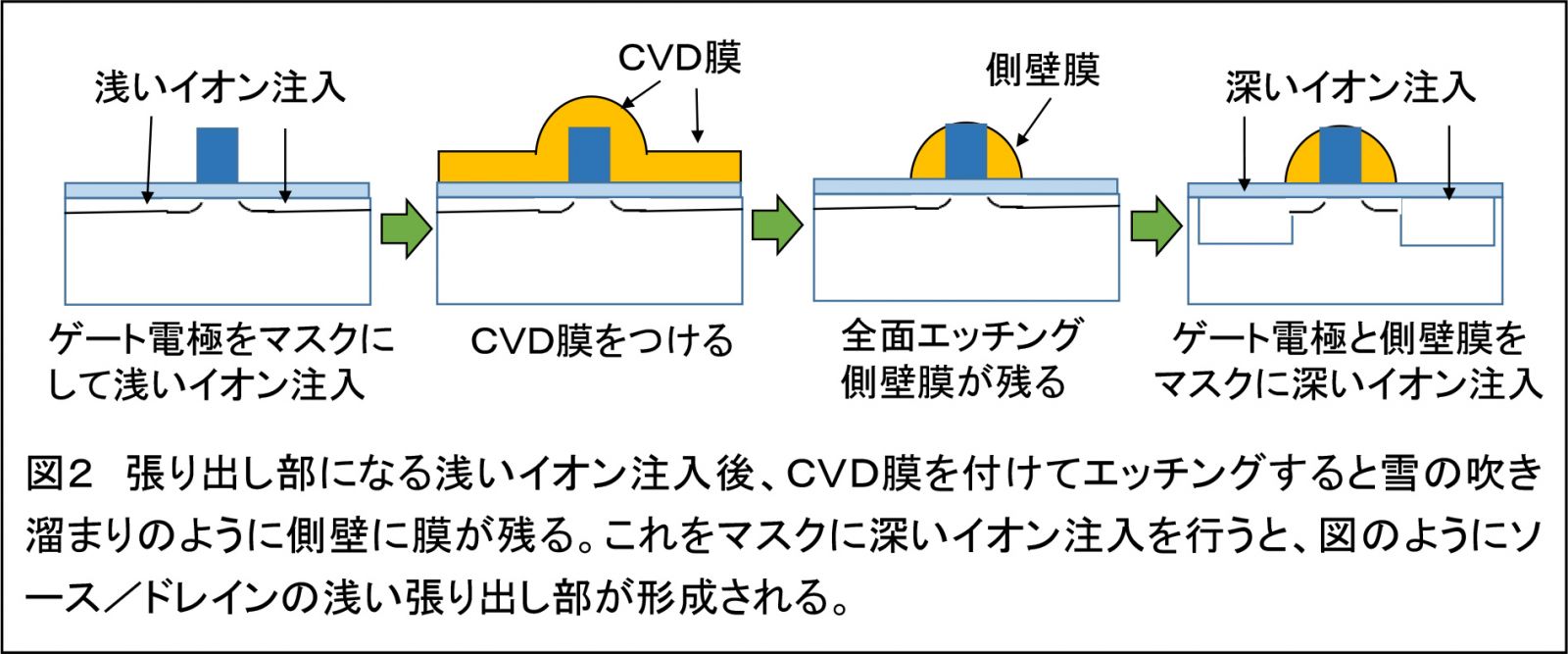

張り出し部分を作成する方法は中々巧妙である。図2のように浅いイオン注入を行い、次いでCVD膜(主にSiO2)をデポジットした後、そのままエッチングして膜を取ってしまう。ところがCVD膜はゲート電極の側壁に雪の吹き溜まりのように厚くついているので、全面エッチングしても側壁膜が残ってくれる。この側壁膜をマスクにして深いイオン注入を行うと、図2のように張り出し部分が形成される。

3. 配線のCR時定数の増加

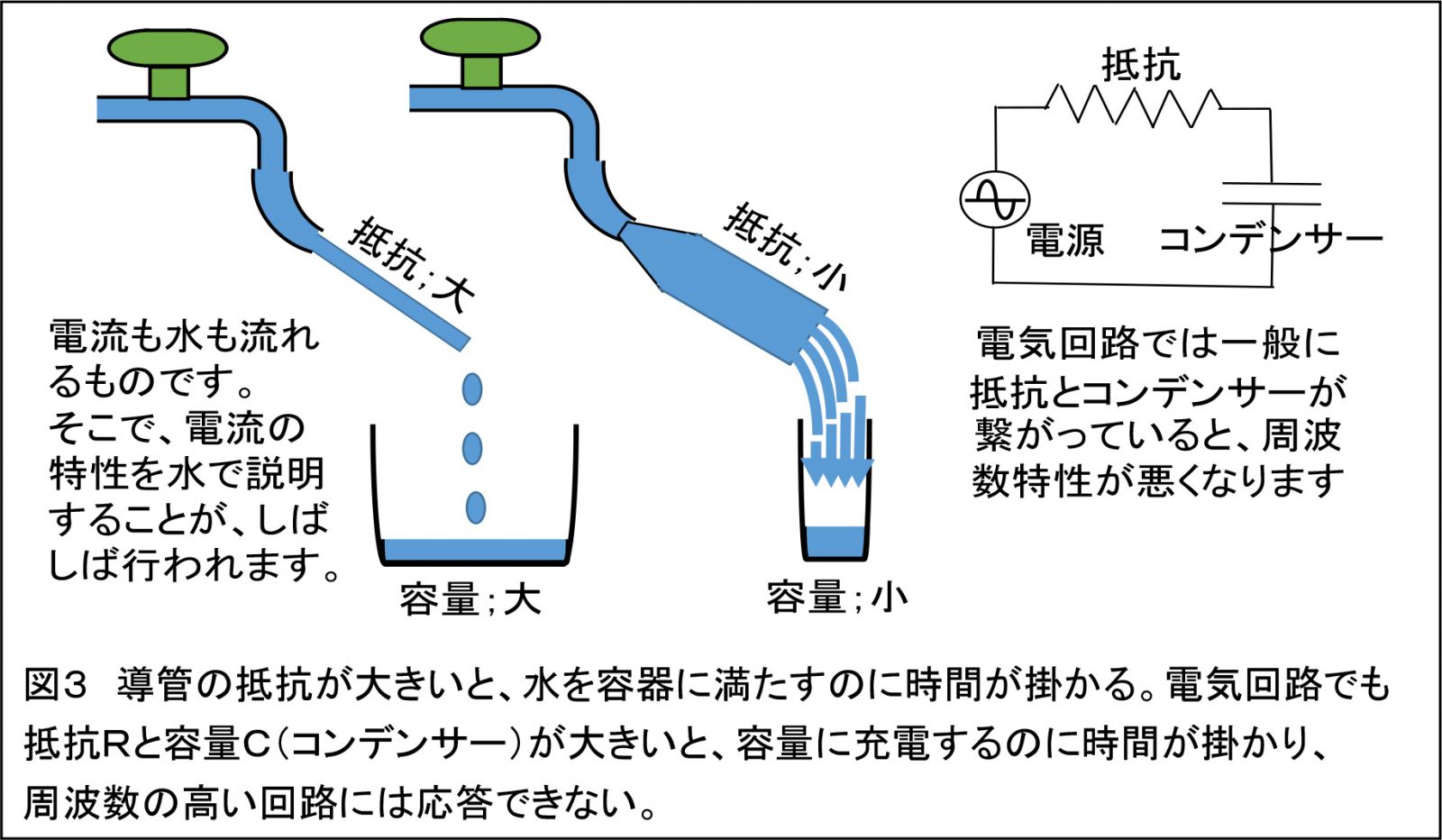

一般の電子回路では、必ず抵抗Rと容量C(コンデンサー)がついて回る問題である。すなわち、配線には超伝導でも用いない限り寄生抵抗があり、配線間や素子間には容量が発生する。このRとCが周波数特性を悪化させる。この関係を水で容器を満たす例で示したのが図3で、導水管が細くて流水の抵抗が大きく、水を貯める容器が大きいと満杯にするには時間がかかる。電気回路では、プラスの電圧が掛かっている間に容量Cに充電し切れず、極性がマイナスに代わると追従できないことになる。従って、高周波回路では、CとRの値を小さくすることは重要である。

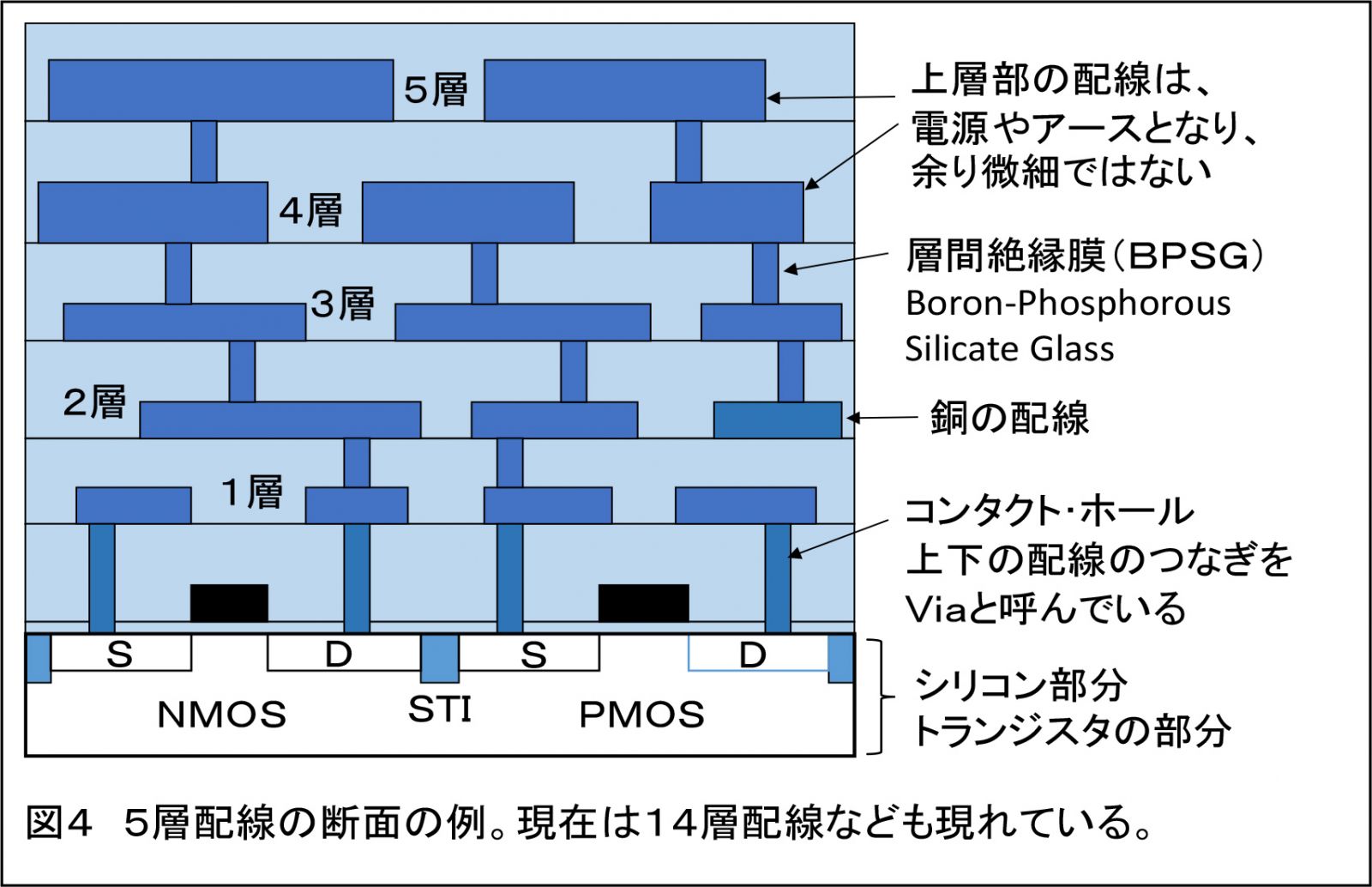

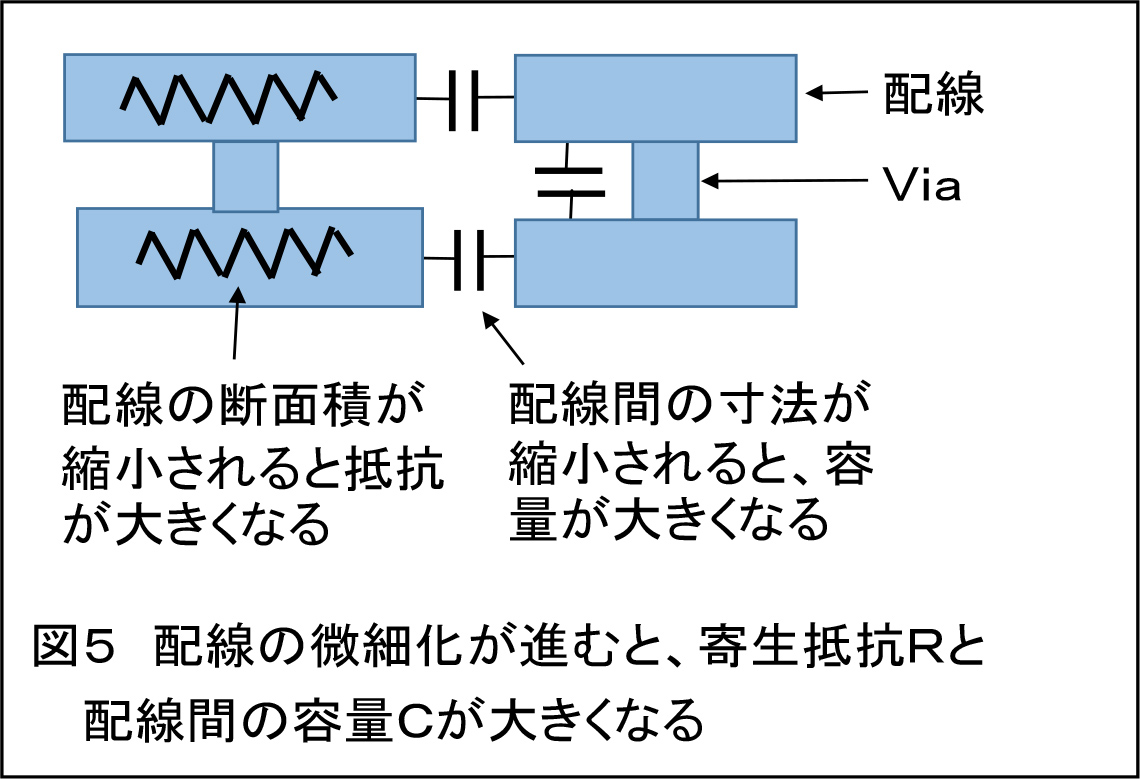

さて、LSIの配線構造は図4のように多層で、今や14層のLSIも出現している。LSIの微細化に対応して、配線の寸法も微細化が進んで、20nmから10nmの時代になりつつある。配線が微細化されると、抵抗値は断面積に反比例するので図5のように配線抵抗が大きくなり、配線間の容量も層間の距離が縮小すると大きくなる。比例縮小則では、LSIが微細化されると周波数特性が向上することになっていたが、それはトランジスタについてのことであって、配線に関しては100nm以下の微細化LSIでは、周波数特性が向上しないどころか悪化する可能性があり大きな問題となった。

- 会社名

- 厚木エレクトロニクス

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

アレムコの導電性/熱伝導性接着剤,コーティング材,グリースのことなら(株)エス・エス・アイ株式会社エス・エスアイ

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

SEMICON Japan 2023 2023年12月13日(水)〜15日(金)の3日間、東京ビッグサイトにおいて、半導体を中心としたマイクロエレクトロニクスの製造を支える装置/材料産業の総合イベントであるSEMICON Japan 2023が開催された。Gichoビジネスコミュニケーションズ株式会社