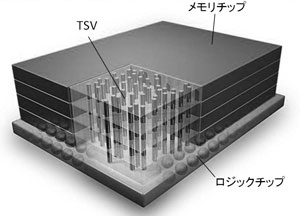

マイクロバンプとハブリッドボンディング

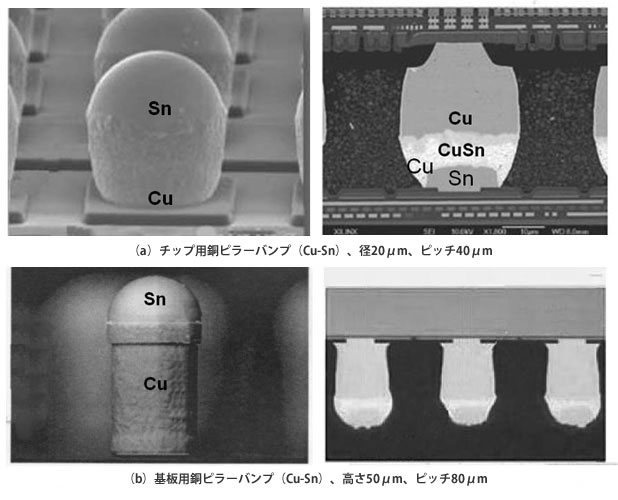

ワイドIOなどの開発でTSVの必要数が増加して、必然的にバンプピッチが小さくなり、フリップチップ時代は150μm以上だったピッチは最近は40?50μm前後になりつつあり、従ってバンプ直径は20?25μm程度が標準になりつつある。微小ピッチでははんだ材(熔融金属)が隣のバンプと接触するのを防ぐためはんだ量は少なくなるが、バンプ高さを保持するためには図7(a)に示すように、棒状の銅ピラー(柱)をたて、はんだ材には主としてSnを使う。他にSnAg、Au、Inなども報告されている。 Snはボンディング時にCuと合金を作り、少量のために図のように全体がSn-CuのIMC(金属間化合物)になり、一般に融点が高くなる。従ってボンディング後は再度融点まで上げてもSnは熔解しない。チップを有機基板へボンディングする場合は基板の凹凸を吸収するためにCuピラーを更に高くする。それらの例を図7(b)にしめす。

図7 マイクロバンプとボンディング状態

3Dデバイスの積層にはチップ−チップ(C to C)、チップ−ウエハ(C to W)、ウエハ−ウエハ(W to W)が提案されているが、歩留まりとコストを考えるとC to Wが現実的であり、今後はマイクロバンプ付きチップをウエハ、またはウエハ上のチップにボンディングするのが標準となるであろう。マイクロバンプの大きさから見てチップ間の隙間が数μmまで狭くなると、従来の液状アンダーフイルの注入は困難になる。そのためボンディング前に下側ウエハに接着用の液状樹脂を塗布し、または樹脂フィルムを貼付しておき、ボンディング時の加熱により軟化して低粘度になり、ボンディング終了後硬化してそのまま間隙を保護する。上側チップに樹脂を着ける工法も提案されている。これらのプロセスをハイブリッドボンディングと呼び、加熱温度、硬化プロセスなどが検討されている。今後は恐らくボンディングの標準工程となるであろう。

マイクロバンプでは大型バンプに比べてボンディング強度が低下する。さらにIMC化されることではんだ材が硬化し、柔らかいはんだ材によるひずみの吸収がなくなるので強度はより低下する。また有機基板とチップの熱膨張係数差からワーページ(反り)が発生し、厚いチップの方がひずみに順応できない。3D構造では厚さの異なるチップを積層すると、上方のチップが厚いほどヒートサイクル試験でバンプが破壊しやすく、薄いチップの方が破壊しにくいことが報告されている。上述の2.5D構造ではチップが分離しているために複雑な状態になることが考えられる。3Dのパッケージングに際してはボンディング時、ICF硬化時、モールド時、基板搭載のリフロー時、動作時などいくつかの温度環境を通過するのでワーページに対する検討が必要とされている。

チップ間保護用インターチップフイル

上述のハイブリッドボンディングに於いては、樹脂材料の選定がきわめて重要である。接着強度の強いことは当然重要であるが、その他にもガラス転移温度とボンディング温度との関連、ボンディングの位置合わせのために透明性を良くし、また樹脂内にフラックス作用をもつ材料を含ませる。熱膨張係数の調整用にシリカフィラーを60%程度混入し、3D構造で問題になる熱の発生に対応しては熱伝導度を良くするBN粉などを導入し、ボンディング前に適度のBステージ化を行って流れ性を制御してバンプの保護作用をもたせることや、ウエハ貼付後のダイシング適性など各種の特性が要求されている。

現在発表されている材料としてはOBAR(Over Bump Applied Resin)、BNUF(Bstageable No Flow Underfill)、HT-ICF(High Temperature ICF)、WAUF(Wafer Level Underfill)などがあるが、全体としてインタチップフイル(ICF)と呼ばれ、チップ積層時の重要な技術課題として材料メーカーなどで活発に研究されている。

< 参 考 資 料>

1.IBM Presentation, “3D Copper TSV Integration,Testing and Reliability” IEDM 2011, No.7-1, Dec.5,2011

2.エルピーダプレスリリース、2011.12.28

3.Banijamali, “Advanced Reliability Study of TSV Interposers and Interconnects for the 28nm Technology FPGA” ECTC 2011, p285

4. Roullard, “Evaluation of 3D Interconnect Routing and Stacking Strategy to Optimize High Speed Signal Transmission for Memory on Logic” ECTC 2012, p8

5.IBM and Micron, Press Release, 2011, Dec.01

- 会社名

- 長野実装フォーラム

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

アレムコの導電性/熱伝導性接着剤,コーティング材,グリースのことなら(株)エス・エス・アイ株式会社エス・エスアイ

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

SEMICON Japan 2023 2023年12月13日(水)〜15日(金)の3日間、東京ビッグサイトにおいて、半導体を中心としたマイクロエレクトロニクスの製造を支える装置/材料産業の総合イベントであるSEMICON Japan 2023が開催された。Gichoビジネスコミュニケーションズ株式会社