1. 緒言

「半導体の集積密度は2年ごとに2倍になる」という、いわゆるムーアの法則は、およそ半世紀にわたってエレクトロニクス業界の技術開発を考える上での指針となってきた。

しかし、プロセスの微細化による密度向上という方向性では、この法則には物理的な限界があることが衆目の一致するところであり、そのためチップを縦に集積する三次元化技術が注目されている。

TSV(Through Silicon Via、シリコン貫通電極)及びTGV(Through Glass Via、ガラス貫通電極)はこの三次元パッケージにおいて、積層されたチップ上にある回路を接続するための、あるいは表面のデバイスを裏面の次階層接合部(はんだボールなど)へ接続するための重要な技術である。

このTSV・TGVネットワークを可能にするのが、高いアスペクト比を持つ狭小ビア内を成膜するALD(Atomic Layer Deposition、原子層堆積)技術である。

2. TSV・TGVを利用した接続

チップから外部への電気的接続にはいくつかの種類がある。

代表的なものがワイヤを用いて集積回路上の電極からパッケージやプリント基板へ接続するワイヤボンディング技術である。

自由度が高くコストが低いものの、ボンディングパッドが大きな面積を占める、ワイヤが長いため高周波での信号減衰や信号波形の劣化、及び電力消費が大きいといった問題がある。

フリップチップ技術はチップを上下逆さまにして電極を下向きにすることで、チップ表面全体で接続を可能にし、かつ接続長さを短くできる。

但しフリップチップでは基本的に表面電極だけなので積層ができない。

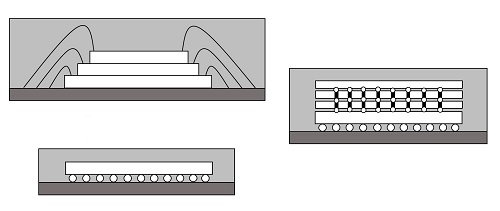

積層されたチップを貫通するTSVを使用することで、高密度・小面積・優れた高周波動作性・低消費電力を実現することができる(図1)。

図1 接続方式の比較

またシリコンウエハではなくガラス基板が用いられる場合はThrough Glass ViaすなわちTGVとなる。

ガラス材料は絶縁性が高く、伝送損失が低く高周波特性に優れる特性があるため、5G時代に向けたRFデバイス開発でも有用とみなされている。

3. ビア内成膜プロセス概要

TSVプロセスではビア開孔を回路作成の前にするか後にするか(ビアファースト・ビアラスト)、表面ビアか裏面ビアか、また開孔をボッシュプロセスにするかレーザにするか、さらに薄化プロセスなど、押さえておかなくてはならない技術が種々あるが、本稿では成膜のみに照準を絞って述べる。

全体の工程の詳細については文末の参考文献リストを参照願いたい。

まず導通させるためには、ビア内には導電体を埋め込む必要があり、これは通常Cuの電解めっきで行われる。

めっきも湿式の成膜であるが、詳細は割愛する。

本稿の焦点はめっき下地の成膜である。

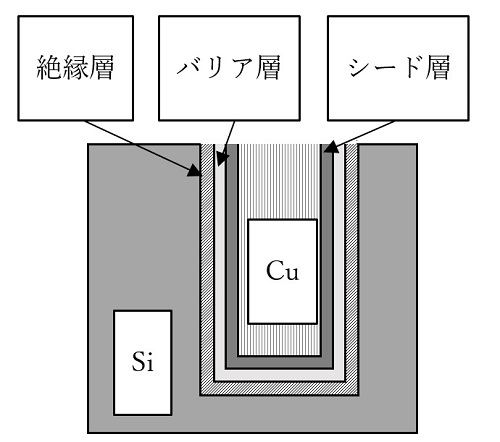

TSVの場合、基板とめっき層の間には一般的に三層の薄膜形成がなされる。

まず一番下地には絶縁層、ついで銅の拡散を防ぐためのバリア層、最後に銅めっきの電極となるシード層が必要である(図2)。

図2 TSV内部成膜積層構造(※簡便のため縮尺は考慮していない)

ただ、必ずしも「共通」の層構成があるわけではない。

TGVの場合、一般的なガラスは絶縁体であるため絶縁層は必要ないと考えられ、またビア内導電体としてタングステンやポリシリコン、あるいは導電ペーストを使用することで導電性は低下するもののCu拡散バリア層が必要ではなくなる(Cuを使った場合でもアプリケーションによってはバリア層が必要なほど拡散はしないケースもある)。

世の中には下地成膜をせず、触媒を付着させて直接めっきする無電解めっきというものも存在しており、膜の構成やプロセスはまさに千差万別である。

膜構成を決める上で重要なポイントが密着性である。

特に平滑なガラス表面に対してのめっき層の密着性は一般に良くなく、接着層の成膜がひとつのカギとなる。

また成膜の難易度はアスペクト比と比例して上がる。

TSV・TGVではビアのアスペクト比は大凡5~20程度と言われているが、このレベルではスパッタなどPVDではほとんどビア開口部周辺のみしか成膜されない(※)。

CVDでは成膜はできるもののカバレッジがいいとはいえず、開口部から遠くなると顕著に膜厚が落ちる。

(※)垂直ビアの場合。

テーパー型などの場合にはアスペクト比が下がるため底部まで届きうるが、やはり奥に入るほど膜厚は大きく低下する

4. ALDによるビア成膜の特徴

ALD技術については本誌でも数回述べてきたが、以下に簡単に特徴を述べる。

技術詳細については参考文献をご参照いただきたい。

① 膜質が化学量論比に近く非常に緻密であり、ピンホールフリー

② 素地への密着性が高い

③ 複雑な3D形状物やナノスケール表面(高ARトレンチ・ナノポアなど)へも均一に成膜できる

④ 再現性の高いプロセスとして膜厚を厳密にコントロールできる

⑤ 比較的低温での成膜が可能で、基板へのダメージを低減できる

これらの特色のうち、ビア成膜に関しては特に③の高アスペクト比への均一成膜が強みをもつ。

成膜可能なアスペクト比の大凡の目安では、PVDの場合は1、CVDでは10に対して、ALDでは100以上(Picosunの装置では1000以上も可能)である。

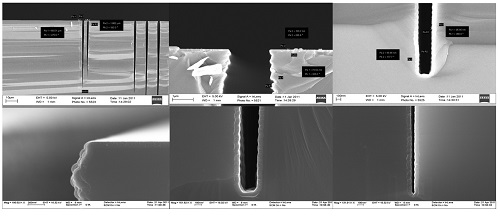

またステップカバレッジも非常に優れており(図3)、CVDでAR10未満でも50%程度に対し、ALDではAR60で>90%というデータがある(※)。

図3 ALDによるビア内成膜断面SEM写真

まためっき下地として、②の密着性はきわめて重要であるが、ALDの場合、膜は基板表面に化学吸着(共有結合)するため密着力が高く、接着層としての使用には最適である。

さらにビアラストと呼ばれる、回路形成後にビア加工をする場合には⑤の低温成膜が有用である。

さらに、1項で述べた多様な材料の膜を1チャンバ内で真空を破らず連続成膜できるのも特徴である。

ALDはプリカーサと呼ばれるガス原料をリアクションチャンバへ導入し、基板表面に吸着させて成膜する。

プリカーサA→パージ(排気)→プリカーサB→パージのサイクルを繰り返して膜厚を増やしていくが、膜材料を変更するにはガスラインを切り替えるだけなので簡便であり、異なる材料の積層(ナノラミネート)もバリア層などではごく一般的に使われる技術である。

(※)https://www.enas.fraunhofer.de/content/dam/enas/

en/documents/Downloads/Data%20sheets/TSV_JP_web.pdf

5. TSV・TGV成膜用ALDプロセス設計のポイント

ALDプロセス設計のポイントは大きく3つある。

(1)材料選定

ある材料でALD成膜が可能かどうかは、適したプリカーサがあるかどうかに大きくかかっている。

ALDのプリカーサとして使用するには、揮発性であること、プロセス中に熱分解しないこと、吸着後に自己制御性を満たすこと、酸化剤・窒化剤など対となるプリカーサと反応すること等の条件があり、例えばシード層としてスパッタで良好であった材料であっても、そのままALDで使うのは難しい場合もある。

また同じ材料を成膜するにも複数のプリカーサが存在する場合があり、プリカーサによって使用条件や膜質が変わってくる。

そのため化学品の特性を理解してターゲットの性能・プロセス条件から選定しなくてはならない。

(2)プロセスパラメータ設定

サイクル時間や温度、その他のプロセスパラメータを適切に設定することは、ALD膜の性能を発揮させるために重要である。

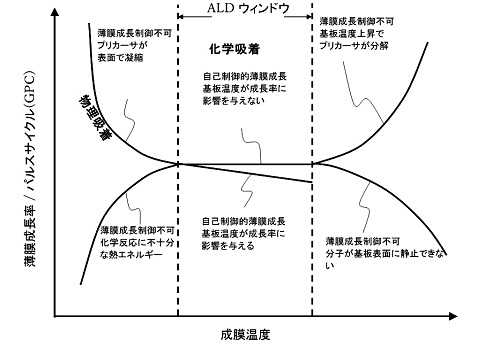

成膜温度によって電気・光学特性が変わることはよく知られているが、適切なパラメータの設定ができていないとALDの特徴である化学吸着ができず物理吸着となり、密着力が低下し剥がれの原因となることもある(図4)。

図4 ALDウインドウ

(3)装置選定

適切な材料を選定し、適切なパラメータを理解していたとしても、それらを適切に組み合わせることのできる装置がなくてはプロセスは実現できない。

またALDは既に研究室向けの技術ではなくなっており、量産工程まで視野に入れた場合には、ランニングコスト、プロセスの再現性、オペレーションの安全性なども重要である。

6. 結言

本稿に述べた通り、TSV・TGVへの成膜は、近年の3D実装・5G対応において重要な技術となっており、アスペクト比の高い表面への付き回り性、表面との密着力などの点で他の成膜方法よりも優れたALDが注目されている。

非常に重要なノウハウであるため、ここでは材料やプロセスの詳細は省略したが、ピコサンでは、絶縁層・バリア層・接着層・シード層いずれもプロセスを確立している。

また量産工程へも幅広い実績があり、本アプリケーションのみならず、ALDソリューションを検討する際にはぜひお声がけいただきたい。

<参考文献>

1)傳田精一(2011)『シリコン貫通電極TSV 半導体の高機能化技術』, 東京電機大学出版局

2)八尋大輔(2019)「インプラント型電子メディカルデバイスへのALD(原子層堆積)法による生体適合膜封止」, エレクトロニクス実装技術Vol.35 No.2

3)八尋大輔(2019)「ALD(原子層堆積)法による成膜」『迫りくるAI時代に向けた半導体プロセスの今』、p118-130, 株式会社情報機構

4)井上浩徳(2016)「スパッタシード層なしガラスへの湿式Cu直接めっきTGV技術」, エレクトロニクス実装技術Vol.32 No.10

- 会社名

- PICOSUN JAPAN(株)

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

アレムコの導電性/熱伝導性接着剤,コーティング材,グリースのことなら(株)エス・エス・アイ株式会社エス・エスアイ

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

SEMICON Japan 2023 2023年12月13日(水)〜15日(金)の3日間、東京ビッグサイトにおいて、半導体を中心としたマイクロエレクトロニクスの製造を支える装置/材料産業の総合イベントであるSEMICON Japan 2023が開催された。Gichoビジネスコミュニケーションズ株式会社