3.連携・コンソーシアム

※各メーカー間の連携、業界コンソーシアムの動きを2010年から示していく。グローバルにSupply Chainを充実させていく展開である。

■2010年

○ Trio forms 3-D chip alliance(6月21日付け EE Times)

→ Elpida Memory社、Powertech Technology社(台湾)及びUMCが、28-nmノードなどのプロセスでのthrough-silicon-vias(TSVs)ベース・三次元(3D)半導体開発を促進するアライアンス設立。

■2011年

○ Elpida, Powertech, UMC team on 3-D at 28-nm(5月31日付け EE Times)

→ Elpida Memory社、Powertech Technology社及びUnited Microelectronics Corp.(UMC)が、28-nmを含む先端製造プロセスに向けた3D IC integration技術を供するthree-wayコラボを最終確定、logic-plus-DRAMへの信頼性のあるアプローチを確立するようthrough-silicon-via(TSV)技術に重点化する。

○ Micron, Samsung seek hybrid memory spec(10月6日付け EE Times)

→ Micron Technology社とSamsung Electronics Co. Ltd.が、hybrid memory cube(HMC)を巡るオープンなコンソーシアム、Hybrid Memory Cube Consortiumの設立を発表、DRAMメモリとロジックプロセスを1つのパッケージに収めて、従来のDRAMに対してパワー効率、バンド幅、密度及びscalabilityの優位性を実現する。HMCは、三次元メモリstacked layersに向けたthrough-silicon-vias(TSVs)が鍵となり、性能を上げ電力消費を下げるinterconnectとなる。

○ Xilinx shipping new FPGA built on TSMC 28nm process(10月27日付け DIGITIMES)

→ 最近の台北でのpress eventにて、Xilinxのworldwide quality and new product introduction、senior VP、Vincent Tong氏。同社が、2.5D IC stacked実装技術による最初の製品、Virtex-7 2000T FPGAを初めて出荷、該半導体はTSMCの28-nm HPL(low power with HKMG)プロセスで製造する。

○ Rambus, ITRI to collaborate on 3-D Packaging(12月15日付け EE Times)

→ 技術licensor、Rambus社(Sunnyvale, Calif.)と台湾のIndustrial Technology Research Institute(ITRI)が、interconnect及び3D実装技術開発でコラボ、当初はSiインタポーザ技術によるシステムintegration開発に重点化、Rambusはまた、ITRIが主導するmultinationalリサーチ association、Advanced Stacked-System Technology and Application Consortium(Ad-STAC)に参画する。

■2012年

○ AMAT, Singapore’s microelectronics institute open 3D semiconductor packaging R&D lab(3月7日付け ELECTROIQ)

→ 半導体fab装置サプライヤ、Applied Materials(AMAT)社が、協力パートナー、シンガポール Agency for Science、Technology and Research(A*STAR)傘下のリサーチ機関、Institute of Microelectronics(IME)とともに新しいCentre of Excellence in Advanced PackagingをシンガポールのScience Park IIにオープンする。

○ Abu Dhabi, Saxony invest in‘twin labs’ 3-D IC project (4月13日付け EE Times)

→ファウンドリ半導体メーカー、Globalfoundries社(Milpitas, Calif.)のmajorityオーナー、Advanced Technology Investment Co.(ATIC)とドイツのState of Saxonyが、ICsの3D stackingをリサーチする一対のラボに$4.8M出資することで合意、この2つのラボは、Abu DhabiのMasdar Institute of Science and Technology及びSaxonyのTechnical University of Dresdenが受けもつ。

○ Dow Corning and Suss cooperate on making 3-D TSV chips (6月26日付け EE Times)

→ 接着及びリリース両方の層から成るDow Corning(Midland, MI)のSi-ベース材料は、bi-layer spin coating及びbondingプロセスの簡単な処理に最適化され、SUSS MicroTec AG(Garching、Germany)の装置と一緒になった全体ソリューションは、標準の製造方法を用いる簡単なbondingの利点が得られ、via middle及びinterposer TSV処理に向けた温度及び化学的要求と両立するとともに、先端実装応用に必要となる室温de-bonding高速化が得られる。

4.標準化

業界コンソーシアムの取り組みとともに、標準化がビジネスの前提となるメモリ関係で活発な活動が見られている。

■2010年

○ SEMI International Standards Program Forms 3D Stacked IC Standards Committee(12月7日付け 3D InCites Press Release)

→SEMIが、Three-Dimensional Stacked Integrated Circuits(3DS-IC)標準化委員会の設立を発表、メンバーは次の通り。

Amkor、ASE、IMEC、ITRI、Olympus、Qualcomm、Semilab、Tokyo Electron、Xilinx

当初は次の3つのTask Forces:Bonded Wafer Pair(BWP) Task Force、Inspection and Metrology Task Force、Thin Wafer Carrier Task Force

○ Sematech, SRC and SIA plan 3-D chip infrastructure(12月8日付け EE Times)

→Sematech、SIA及びSRCが、heterogeneous 3D integrationに向けた業界標準化及び技術的仕様を推進するプログラムを発表。

■2012年

○ Wide I/O driving 3-D with TSV(3月9日付け EE Times Asia)

→ 今年リリースされたJEDECのWide I/O standard for mobile DRAMsには、3D ICパッケージのTSV interconnectsが重要となる。TSVsは当初は1つのパッケージ内でロジックとメモリをつなぐのに用いられるが、アナログ、イメージセンサ、パワー及び高周波デバイスをゆくゆくはつないでいくinterconnect技術となる可能性がある。

○ First 3D-IC Standard Approved(8月7日付け SEMI)

→ 2010年後半に設立されたSEMI 3DS-IC Committeeが、SEMICON West 2012の間に最初となる標準、SEMI 3D1, Terminology for Through Silicon Via Geometrical Metrologyの発行を承認した。この標準は、TSVsの寸法について幾何学的計測標準の出発点となる旨。

おわりに

以上、昨年後半以降、特に活況著しい3次元半導体の技術及び業界動向を述べてきた。当社の技術を一つとして、業界で数多くのアプローチがあり、応用の分野、範囲の広がりの急展開が日々起きている状況である。半導体業界の今後の技術及び製品展開上、ブレイクスルーを図る有力な手段として3次元半導体技術がますます存在感を高めていく流れは必至という現時点である。さらに進化した『グローバルな協調と競争』が、今後の順調な発展・展開に必須である。

- 会社名

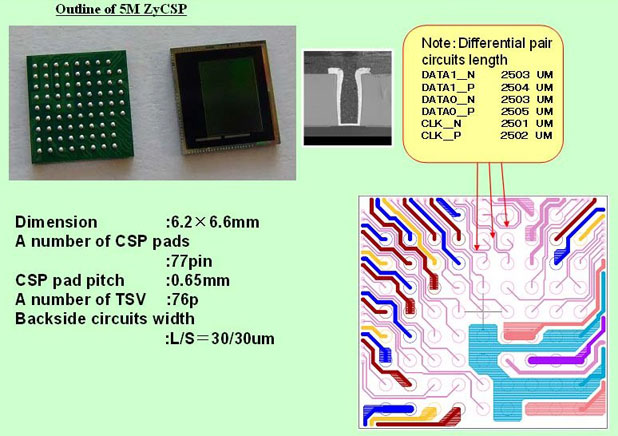

- (株)ザイキューブ

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

アレムコの導電性/熱伝導性接着剤,コーティング材,グリースのことなら(株)エス・エス・アイ株式会社エス・エスアイ

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

SEMICON Japan 2023 2023年12月13日(水)〜15日(金)の3日間、東京ビッグサイトにおいて、半導体を中心としたマイクロエレクトロニクスの製造を支える装置/材料産業の総合イベントであるSEMICON Japan 2023が開催された。Gichoビジネスコミュニケーションズ株式会社