6.Wide I/O規格

2011年の12月に各種規格を制定するJEDECから、まったく新しいモバイル機器用のメモリ規格として、Wide I/O規格が制定されました。

モバイル機器用メモリ規格とは、コンピュータ用のダイナミック・メモリの規格であるDDRメモリ規格(DDR、DDR2、DDR3、DDR4規格)の低消費電力版のメモリ規格です。

モバイル機器用のメモリには低消費電力のほかに機器の小型化が実現できるように要求されます。

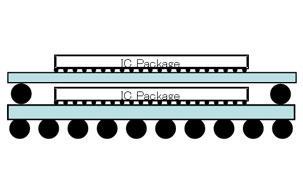

このため、これまでのモバイル用メモリ規格であるLPDDR規格やLPDDR2規格では一般的なコントローラICとメモリを基板上に実装する規格のほか、コントローラICの上にメモリICを実装するためのPoP(Package on Package)実装が規格化されていました(図19)。このWide I/Oメモリ規格では、PoP実装ではなく、コントローラチップの上に直接メモリチップを実装するチップの3D実装が規格化されています(図20)。

図19 PoP(Package on Package)実装

図21 LPDDR3メモリ,(Samsung社 http://japan.samsung.com/newssamsungelectronicsnews/2012/2gb-lpddr3)

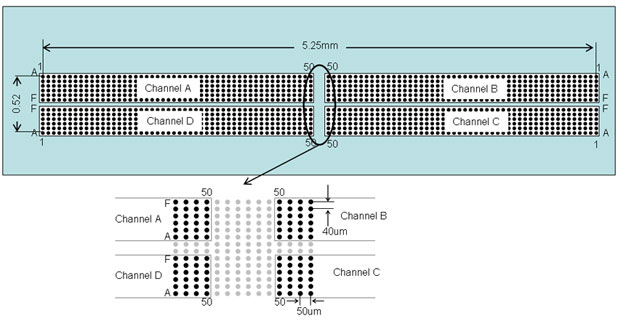

図20 Wide I/Oメモリのパッド配置

ただ、2012年時点では、コントローラチップとメモリチップをTSVを使って、3D実装をした製品をすぐに量産化することは困難だとは、全員が理解していました。

実際、この規格では、ほかのメモリ規格で定められている信号の電気特性については基本的なことしか決定していませんでした。

これは、パッドのピッチや形状、数など3次元実装するための機械的規格を定めて、コントローラやメモリの3次元実装への開発をしやすくし、開発をスピードアップする目的が大きい規格です。

実際、モバイル用メモリとしては、Wide I/O規格より遅れて、昨年5月に規格が規定された、LVDDR3規格のメモリは昨年9月から、すでに製品化されています(図21)。

LVDDR3規格はLVDDR2規格と同じ、PoP実装か基板上の平面実装を使った、LPDDR2規格の高速版です。

一方、Wide I/O規格が定まった昨年は3D実装の熱検討などや、信号試験などTSVの製品化へ向けての発表が、Wide I/O規格でのパッドレイアウトで多く発表されるようになりました。また、2015年には本格的なWide I/Oメモリ規格としてWide I/O 2規格が発表されるといわれています。

現在のWide I/O規格は、クロックの周波数に対してデータの最大周波数は半分となる、SDR(Single Data Rate)の規格です。当然、同じようにロック周波数に対して、SDRはDDRに比べて半分のデータ転送速度にしかなりません。これがWide I/O規格では現在一般に使われているDDR (Double Data Rate)規格になります。本格的な製品版規格のWide I/O 2規格です。

JEDECの規格スケジュールを見ても2015年というのがやはりTSVを使った3D実装の製品化が現実味を帯びてきます。

TSVを使った3D実装実用化までに、これからの1年しかないことになります。このため、最近の発表は実用化を見据えたものが多くなっています。

- 会社名

- (株)日本サーキット|KEI Systems

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

アレムコの導電性/熱伝導性接着剤,コーティング材,グリースのことなら(株)エス・エス・アイ株式会社エス・エスアイ

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

SEMICON Japan 2023 2023年12月13日(水)〜15日(金)の3日間、東京ビッグサイトにおいて、半導体を中心としたマイクロエレクトロニクスの製造を支える装置/材料産業の総合イベントであるSEMICON Japan 2023が開催された。Gichoビジネスコミュニケーションズ株式会社