1.TSVの普及へ

最近、TSV(Through Silicon Via)への関心が特に高まっています。

実装に関連する学会や、コンベンション、セミナーなどでは、必ずといってよいほどTSV関連の発表、講演があります。

たとえば、日本では今年1月に開かれた『ネプコン ジャパン2013』では、『インターネプコンジャパン』と『半導体パッケージング技術展』での技術セミナーは3次元実装、TSVの話題が目白押しでした。

これはアメリカでも同じで、日本よりも積極的に、多くの発表がなされています。

昨年夏のICのコンベンションHotChipsではTutorialとしてTSVの講演が組まれていましたし、パッケージのシンポジウムIMAPS(International Symposium on Microelectronics)やDesignCon、IEEEのECTC(IEEE Electronic Components and Technology Conference)など、どのコンベンションでも必ずTSVの発表がいくつかはあります。

今後の技術動向として、半導体チップの3次元実装は必然的な流れとなっていることは誰もが認めるところです。

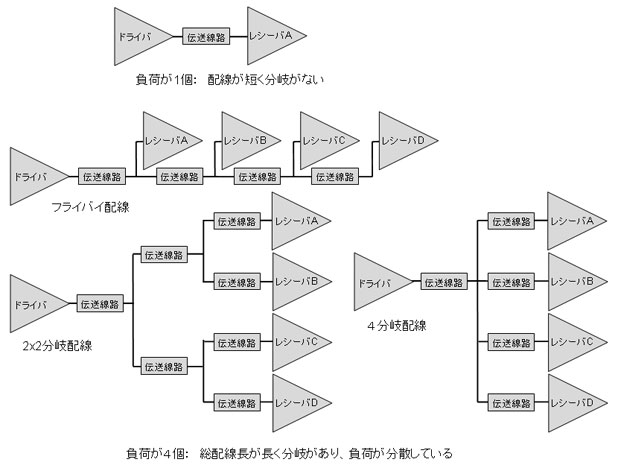

たとえば、モバイル機器からサーバ、スーパーコンピュータまで、すべての機器で使用するメモリの量は急激に増えています。それに対して、メモリのチップ容量の増加はDDRでは回路は究極まで簡単化され、ICの微細化によるも増加だけです。チップ容量の増加は、要求の増加に比較して、遅々としたものです。しかも、データの転送速度の高速化のため、多くのチップをメモリバスに接続すると信号波形が乱れてしまい、接続できるメモリチップの数を増やすことは困難です(図1)。

図1 負荷が多いと波形が乱れる

メモリの容量を2倍、4倍と飛躍的に増加させる方法として、メモリチップを3次元実装が解決になります。

TSVを使ってメモリチップを3次元実装すれば、伝送線路的に見れば、メモリ間の接続は非常に短くなり、伝送路的には1つの負荷に見えるので、2個、4個の接続することができるはずです。

DDR4メモリや携帯機器用の新しいメモリであるWide I/Oメモリなどは、メモリのスタック実装が前提となった規格となっています。

シリアルデータ転送でも28Gbpsなどという高速伝送が現実となりつつあり、ここでは、銅か光かが競合しています。光伝送のためにはドライバのレーザICとレシーバのフォトICが必要となります。光伝送が銅に劣る点はこれらの光ICの価格とシステムの集積度です。

光ICとCMOSによる論理ICでは、その材料の構造が異なります。このように材質や構造がことなるICをヘテロジニアスICと呼び、研究が盛んに行われています。

しかし、残念ながらまだヘテロジニアスICは単一構造のモノジニアスICに比べ、コスト、集積度、性能で劣っているのが現状です。

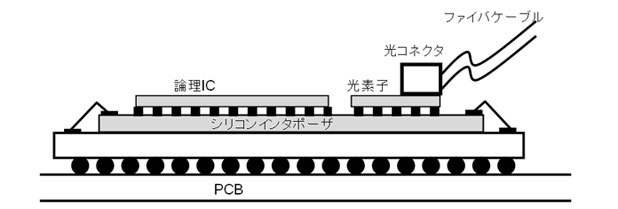

このヘテロジニアスICをモノジニアスで作成しようとして、シリコンインタポーザを使って2.5次元実装したMCMが作成されています(図2)

図2 ヘテロジニアスMCM

- 会社名

- (株)日本サーキット|KEI Systems

- 所在地

-

真空リフロー、N2リフロー、エアリフローのことなら、エイテックテクトロン(株)にお任せください。フラックスレス真空リフロー装置販売開始!エイテックテクトロン株式会社

-

アレムコの導電性/熱伝導性接着剤,コーティング材,グリースのことなら(株)エス・エス・アイ株式会社エス・エスアイ

-

独自の加工技術とノウハウで様々な材料にチャレンジ 〜色々なアイデアを生み出して研究者をサポート〜 ムソー工業株式会社 代表取締役 尾針 徹治 氏Gichoビジネスコミュニケーションズ株式会社

-

SEMICON Japan 2023 2023年12月13日(水)〜15日(金)の3日間、東京ビッグサイトにおいて、半導体を中心としたマイクロエレクトロニクスの製造を支える装置/材料産業の総合イベントであるSEMICON Japan 2023が開催された。Gichoビジネスコミュニケーションズ株式会社